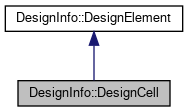

a DesignCell in design netlist, DesignPin objects of which might connect to DesignNet objects More...

#include <DesignInfo.h>

Public Member Functions | |

| DesignCell (const std::string &name, DesignElement *parentPtr, DesignCellType cellType, int id) | |

| Construct a new Design Cell object. More... | |

| DesignCell (const std::string &name, DesignCellType cellType, int id) | |

| Construct a new Design Cell object. More... | |

| DesignCell (bool isVirtual, DesignCellType cellType, int id) | |

| Construct a new Design Cell object without given name. The cell name will be its id string. More... | |

| DesignCell (bool isVirtual, const std::string &name, DesignCellType cellType, int id) | |

| Construct a new Design Cell object. More... | |

| ~DesignCell () | |

| Destroy the Design Cell object and its binded DesignPin objects. More... | |

| DesignCellType | getCellType () |

| void | addPin (DesignPin *_pinPtr) |

| bind a pin to the cell More... | |

| std::vector< DesignPin * > & | getPins () |

| void | addNetForPin (DesignPin *_pinPtr, DesignNet *_netPtr) |

| add a net and assign it into output/input net list More... | |

| std::vector< DesignNet * > & | getOutputNets () |

| std::vector< DesignNet * > & | getInputNets () |

| std::vector< DesignPin * > & | getOutputPins () |

| std::vector< DesignPin * > & | getInputPins () |

| bool | isLUT6 () |

| bool | isLUT () |

| bool | isFF () |

| bool | isLUTRAM () |

| bool | originallyIsLUTRAM () |

| bool | isBRAM () |

| bool | isMux () |

| bool | isCarry () |

| bool | isShift () |

| bool | isDSP () |

| bool | checkHasDSPReg () |

| bool | isIO () |

| bool | isClockBuffer () |

| bool | isShifter () |

| bool | isTimingEndPoint () |

| check whether the cell is an endpoint in timing graph More... | |

| bool | isLogicRelated () |

| check whether the cell is related to logic computation More... | |

| int | getCellId () |

| Get the Cell Id in the cell list. More... | |

| bool | isVirtualCell () |

| ControlSetInfo * | getControlSetInfo () |

| Get the Control Set Info object of this cell. More... | |

| void | setControlSetInfo (ControlSetInfo *_controlSetInfo) |

| Set the Control Set Info object of this cell. More... | |

| void | setVirtualType (DesignCellType NewCellType) |

| Set the Virtual Type object which might override the actual type in later processing. More... | |

| DesignCellType | getOriCellType () |

| Get the Original Cell Type object defined in the design netlist. More... | |

| void | addClockNet (DesignNet *aClockNet) |

| add a clock net which is connected to this cell for later legalization More... | |

| std::set< DesignNet * > & | getClockNets () |

| Get the clock nets connected to this cell for later legalization. More... | |

| void | setHasDSPReg (bool _hasDSPReg) |

| void | setTimingLength (int _timingLength) |

| int | getTimingLength () |

Public Member Functions inherited from DesignInfo::DesignElement Public Member Functions inherited from DesignInfo::DesignElement | |

| DesignElement (const std::string &name, DesignElement *parentPtr, DesignElementType type, int id) | |

| DesignElement (const std::string &name, DesignElementType type, int id) | |

| DesignElement (bool isVirtual, DesignElementType type, int id) | |

| DesignElement (bool isVirtual, const std::string &_name, DesignElementType type, int id) | |

| virtual | ~DesignElement () |

| const std::string & | getName () const |

| DesignElement * | getParentPtr () |

| DesignElementType | getElementType () |

| int | getElementIdInType () |

Private Attributes | |

| std::vector< DesignPin * > | pinPtrs |

| std::vector< DesignPin * > | inputPinPtrs |

| std::vector< DesignPin * > | outputPinPtrs |

| std::vector< std::string > | pinNames |

| std::vector< DesignNet * > | netPtrs |

| std::vector< DesignNet * > | inputNetPtrs |

| std::vector< DesignNet * > | outputNetPtrs |

| std::set< DesignNet * > | clockNetPtrs |

| std::vector< std::string > | netNames |

| DesignCellType | cellType |

| DesignCellType | oriCellType |

| bool | isVirtual = false |

| bool | hasDSPReg = false |

| ControlSetInfo * | controlSetInfo = nullptr |

| int | timingLength = 0 |

Detailed Description

a DesignCell in design netlist, DesignPin objects of which might connect to DesignNet objects

Definition at line 781 of file DesignInfo.h.

Constructor & Destructor Documentation

◆ DesignCell() [1/4]

|

inline |

Construct a new Design Cell object.

- Parameters

-

name the name of the cell parentPtr the hierarchy parent of the design cell cellType the design cell type (NOT resourse BEL type!) id the id of cell in the cell list

Definition at line 792 of file DesignInfo.h.

◆ DesignCell() [2/4]

|

inline |

Construct a new Design Cell object.

- Parameters

-

name the name of the cell cellType the design cell type (NOT resourse BEL type!) id the id of cell in the cell list

Definition at line 812 of file DesignInfo.h.

◆ DesignCell() [3/4]

|

inline |

Construct a new Design Cell object without given name. The cell name will be its id string.

- Parameters

-

isVirtual indicate whether the cell is a virtual one not in the design netlist cellType the design cell type (NOT resourse BEL type!) id the id of cell in the cell list

Definition at line 833 of file DesignInfo.h.

◆ DesignCell() [4/4]

|

inline |

Construct a new Design Cell object.

- Parameters

-

isVirtual indicate whether the cell is a virtual one not in the design netlist name the name of the cell cellType the design cell type (NOT resourse BEL type!) id the id of cell in the cell list

Definition at line 856 of file DesignInfo.h.

◆ ~DesignCell()

|

inline |

Destroy the Design Cell object and its binded DesignPin objects.

Definition at line 875 of file DesignInfo.h.

Member Function Documentation

◆ addClockNet()

|

inline |

add a clock net which is connected to this cell for later legalization

- Parameters

-

aClockNet

Definition at line 1099 of file DesignInfo.h.

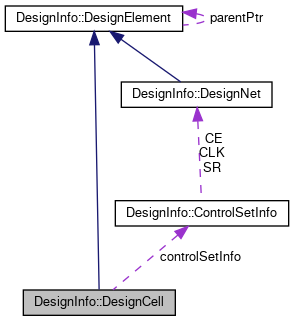

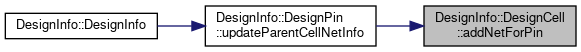

◆ addNetForPin()

add a net and assign it into output/input net list

- Parameters

-

_pinPtr _netPtr

Definition at line 95 of file DesignInfo.cc.

Referenced by DesignInfo::DesignPin::updateParentCellNetInfo().

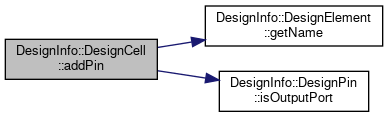

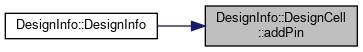

◆ addPin()

| void DesignInfo::DesignCell::addPin | ( | DesignPin * | _pinPtr | ) |

bind a pin to the cell

- Parameters

-

_pinPtr

Definition at line 116 of file DesignInfo.cc.

Referenced by DesignInfo::DesignInfo().

◆ checkHasDSPReg()

|

inline |

Definition at line 975 of file DesignInfo.h.

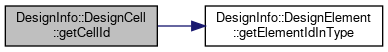

◆ getCellId()

|

inline |

Get the Cell Id in the cell list.

- Returns

- int

Definition at line 1037 of file DesignInfo.h.

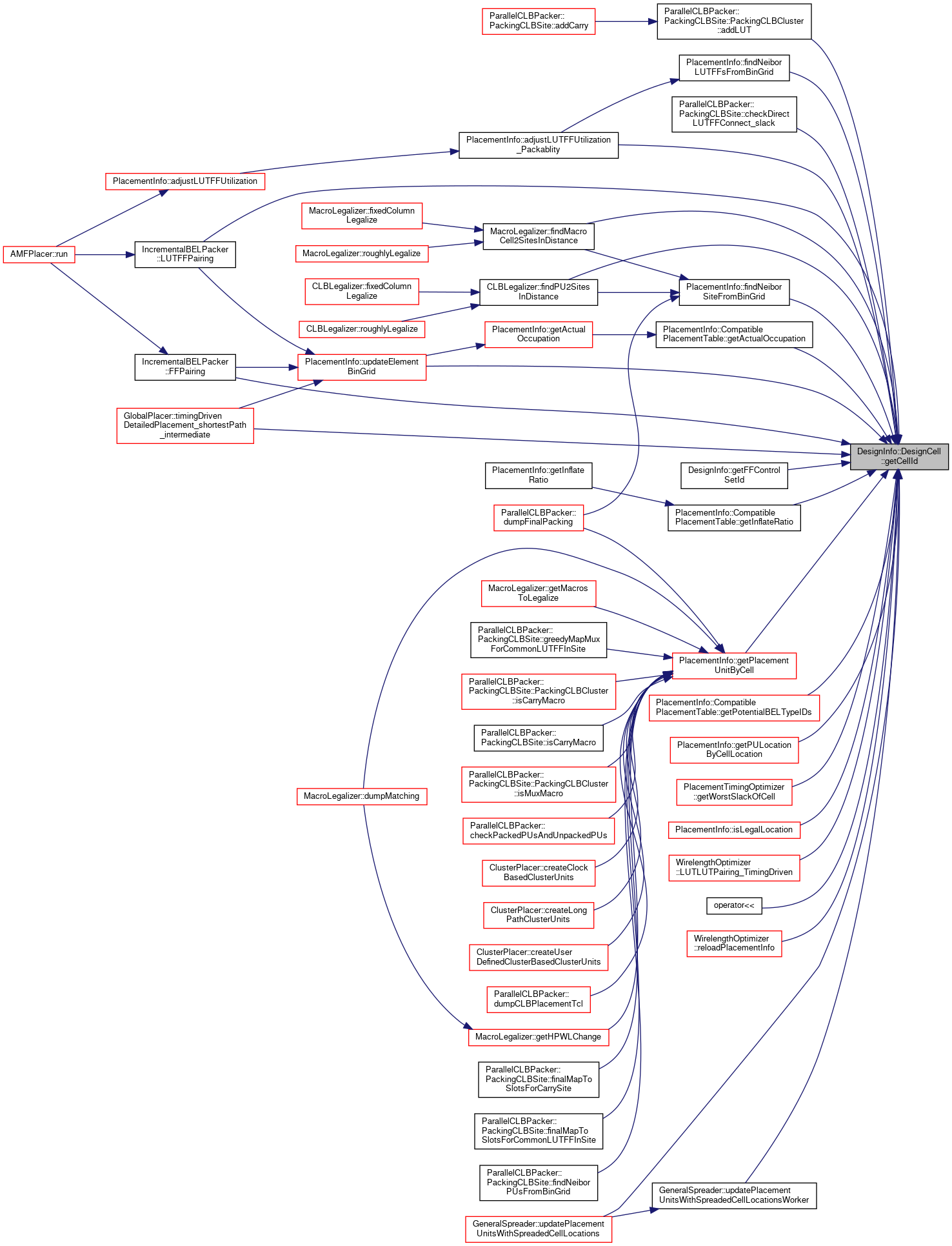

Referenced by ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addLUT(), PlacementInfo::adjustLUTFFUtilization_Packablity(), ParallelCLBPacker::PackingCLBSite::checkDirectLUTFFConnect_slack(), IncrementalBELPacker::FFPairing(), MacroLegalizer::findMacroCell2SitesInDistance(), PlacementInfo::findNeiborLUTFFsFromBinGrid(), PlacementInfo::findNeiborSiteFromBinGrid(), CLBLegalizer::findPU2SitesInDistance(), PlacementInfo::CompatiblePlacementTable::getActualOccupation(), DesignInfo::getFFControlSetId(), PlacementInfo::CompatiblePlacementTable::getInflateRatio(), PlacementInfo::getPlacementUnitByCell(), PlacementInfo::CompatiblePlacementTable::getPotentialBELTypeIDs(), PlacementInfo::getPULocationByCellLocation(), PlacementTimingOptimizer::getWorstSlackOfCell(), PlacementInfo::isLegalLocation(), IncrementalBELPacker::LUTFFPairing(), WirelengthOptimizer::LUTLUTPairing_TimingDriven(), operator<<(), WirelengthOptimizer::reloadPlacementInfo(), GlobalPlacer::timingDrivenDetailedPlacement_shortestPath_intermediate(), PlacementInfo::updateElementBinGrid(), GeneralSpreader::updatePlacementUnitsWithSpreadedCellLocations(), and GeneralSpreader::updatePlacementUnitsWithSpreadedCellLocationsWorker().

◆ getCellType()

|

inline |

Definition at line 881 of file DesignInfo.h.

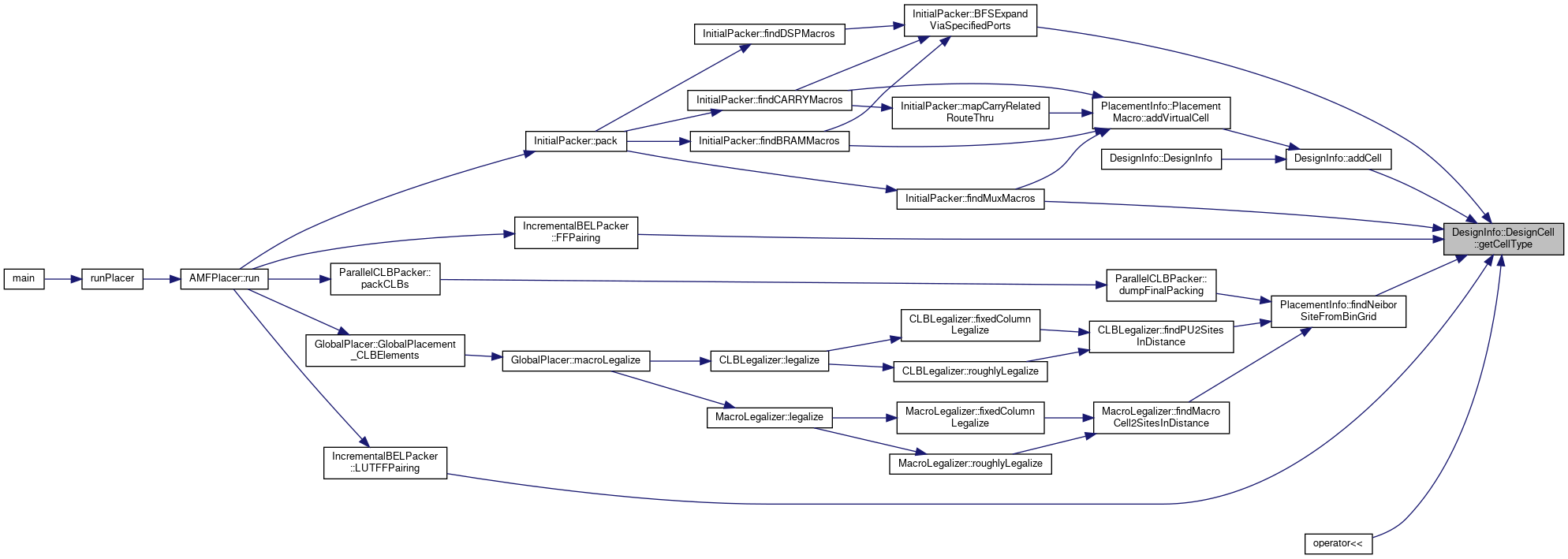

Referenced by DesignInfo::addCell(), InitialPacker::BFSExpandViaSpecifiedPorts(), IncrementalBELPacker::FFPairing(), InitialPacker::findMuxMacros(), PlacementInfo::findNeiborSiteFromBinGrid(), IncrementalBELPacker::LUTFFPairing(), and operator<<().

◆ getClockNets()

|

inline |

Get the clock nets connected to this cell for later legalization.

- Returns

- std::vector<DesignNet *>&

Definition at line 1109 of file DesignInfo.h.

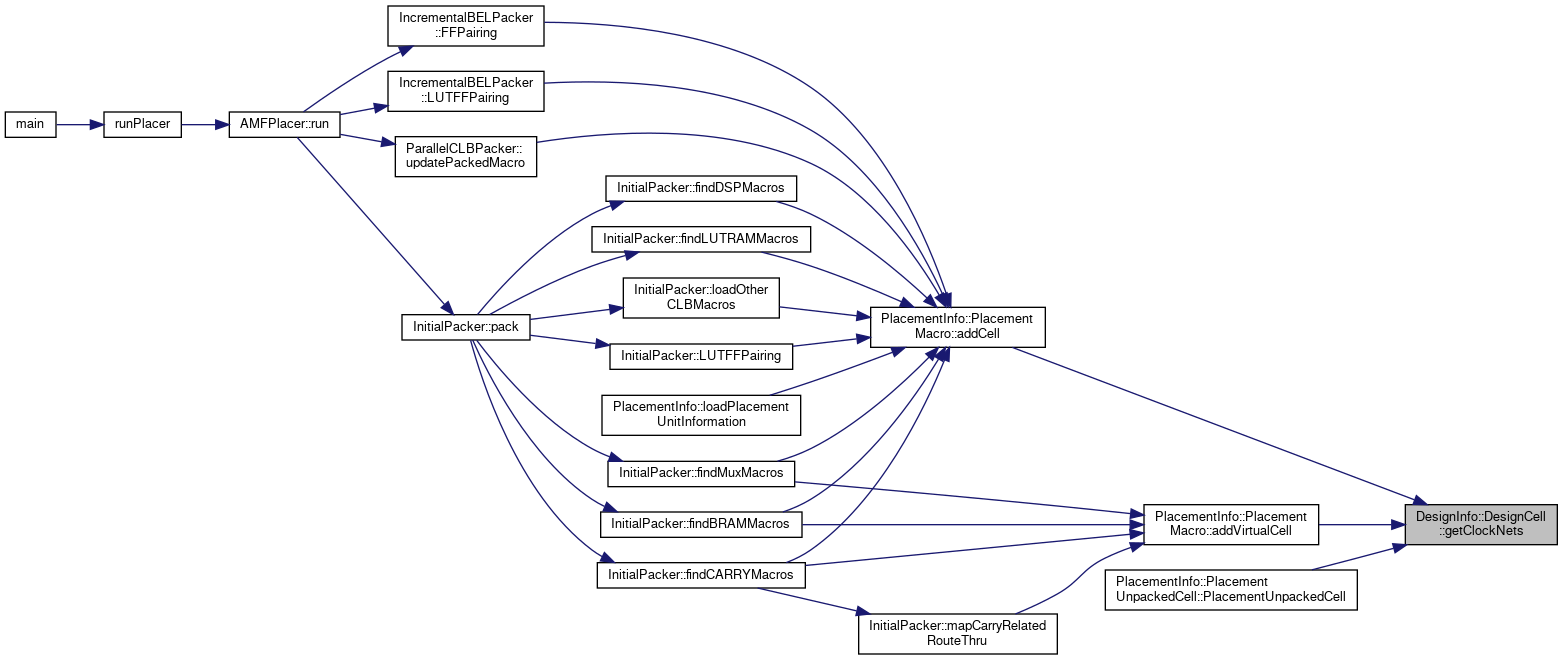

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

◆ getControlSetInfo()

|

inline |

Get the Control Set Info object of this cell.

A control set is a combination of CLK, CE and SR signal. It could be nullptr (not related to control set)

- Returns

- ControlSetInfo*

Definition at line 1054 of file DesignInfo.h.

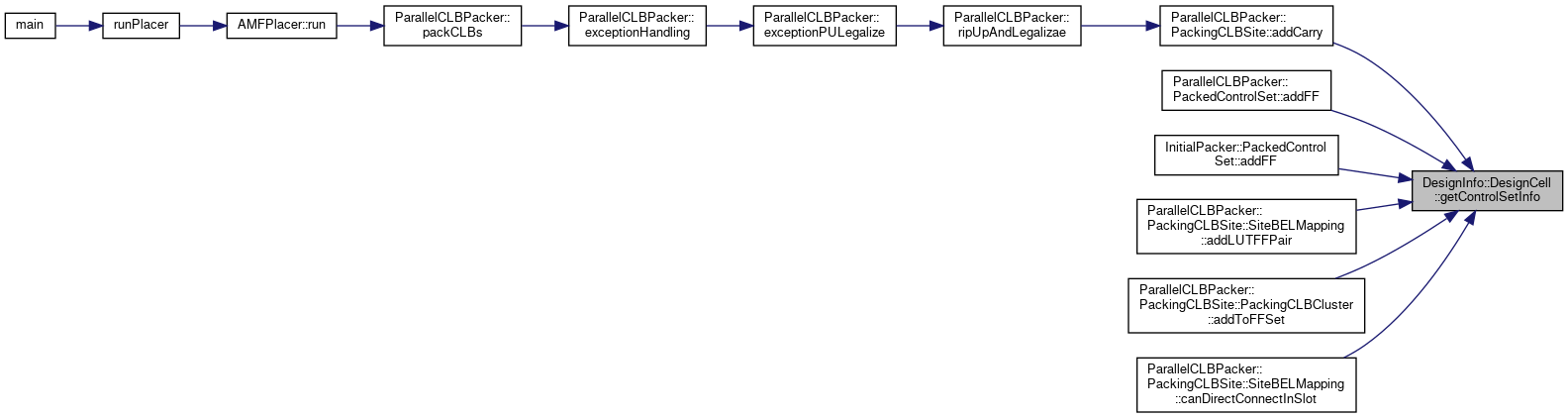

Referenced by ParallelCLBPacker::PackingCLBSite::addCarry(), ParallelCLBPacker::PackedControlSet::addFF(), InitialPacker::PackedControlSet::addFF(), ParallelCLBPacker::PackingCLBSite::SiteBELMapping::addLUTFFPair(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addToFFSet(), and ParallelCLBPacker::PackingCLBSite::SiteBELMapping::canDirectConnectInSlot().

◆ getInputNets()

|

inline |

Definition at line 910 of file DesignInfo.h.

◆ getInputPins()

|

inline |

Definition at line 918 of file DesignInfo.h.

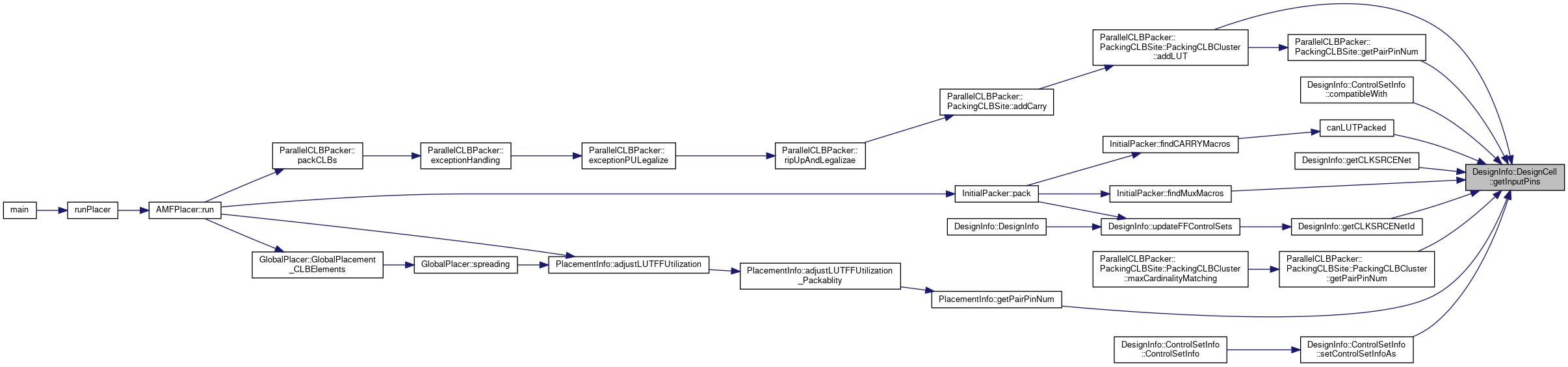

Referenced by ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addLUT(), canLUTPacked(), DesignInfo::ControlSetInfo::compatibleWith(), InitialPacker::findMuxMacros(), DesignInfo::getCLKSRCENet(), DesignInfo::getCLKSRCENetId(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::getPairPinNum(), ParallelCLBPacker::PackingCLBSite::getPairPinNum(), PlacementInfo::getPairPinNum(), and DesignInfo::ControlSetInfo::setControlSetInfoAs().

◆ getOriCellType()

|

inline |

Get the Original Cell Type object defined in the design netlist.

- Returns

- DesignCellType

Definition at line 1089 of file DesignInfo.h.

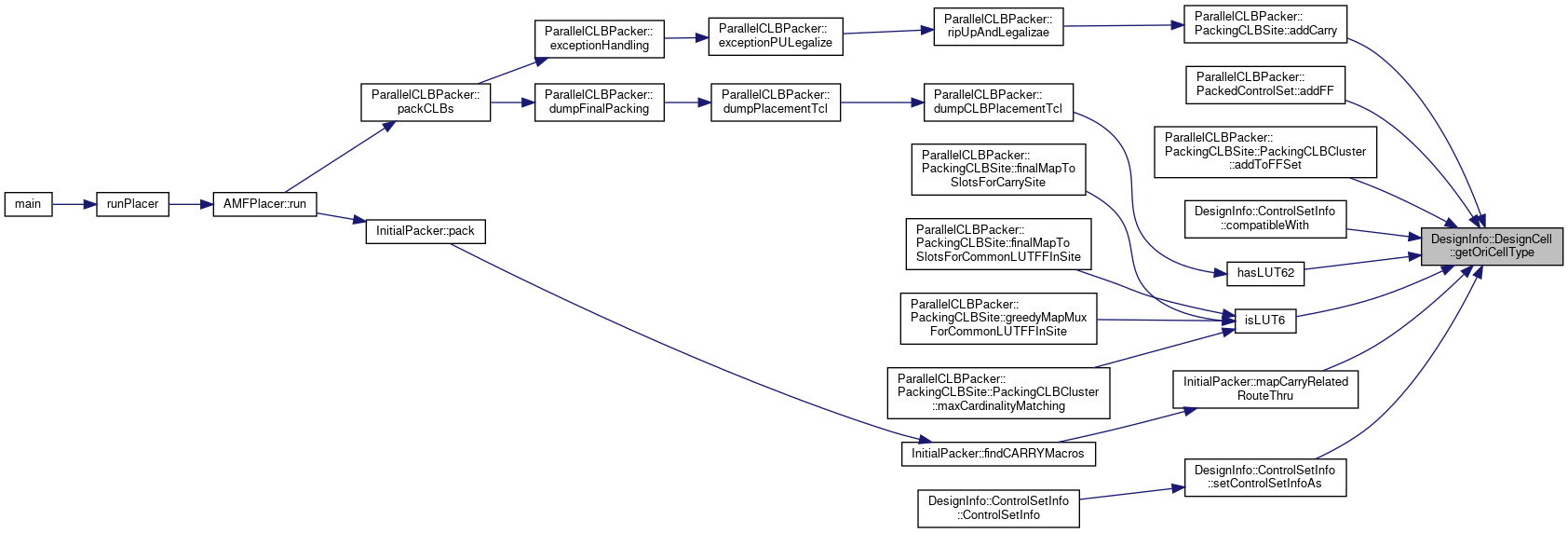

Referenced by ParallelCLBPacker::PackingCLBSite::addCarry(), ParallelCLBPacker::PackedControlSet::addFF(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addToFFSet(), DesignInfo::ControlSetInfo::compatibleWith(), hasLUT62(), isLUT6(), InitialPacker::mapCarryRelatedRouteThru(), and DesignInfo::ControlSetInfo::setControlSetInfoAs().

◆ getOutputNets()

|

inline |

Definition at line 906 of file DesignInfo.h.

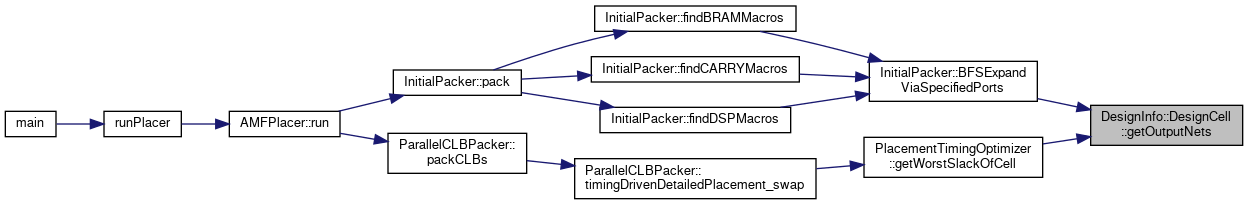

Referenced by InitialPacker::BFSExpandViaSpecifiedPorts(), and PlacementTimingOptimizer::getWorstSlackOfCell().

◆ getOutputPins()

|

inline |

Definition at line 914 of file DesignInfo.h.

Referenced by IncrementalBELPacker::LUTFFPairing().

◆ getPins()

|

inline |

Definition at line 893 of file DesignInfo.h.

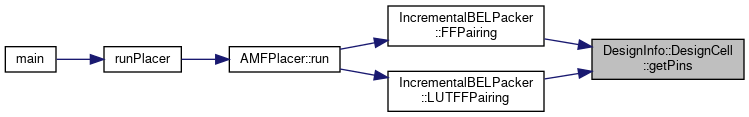

Referenced by IncrementalBELPacker::FFPairing(), and IncrementalBELPacker::LUTFFPairing().

◆ getTimingLength()

|

inline |

Definition at line 1124 of file DesignInfo.h.

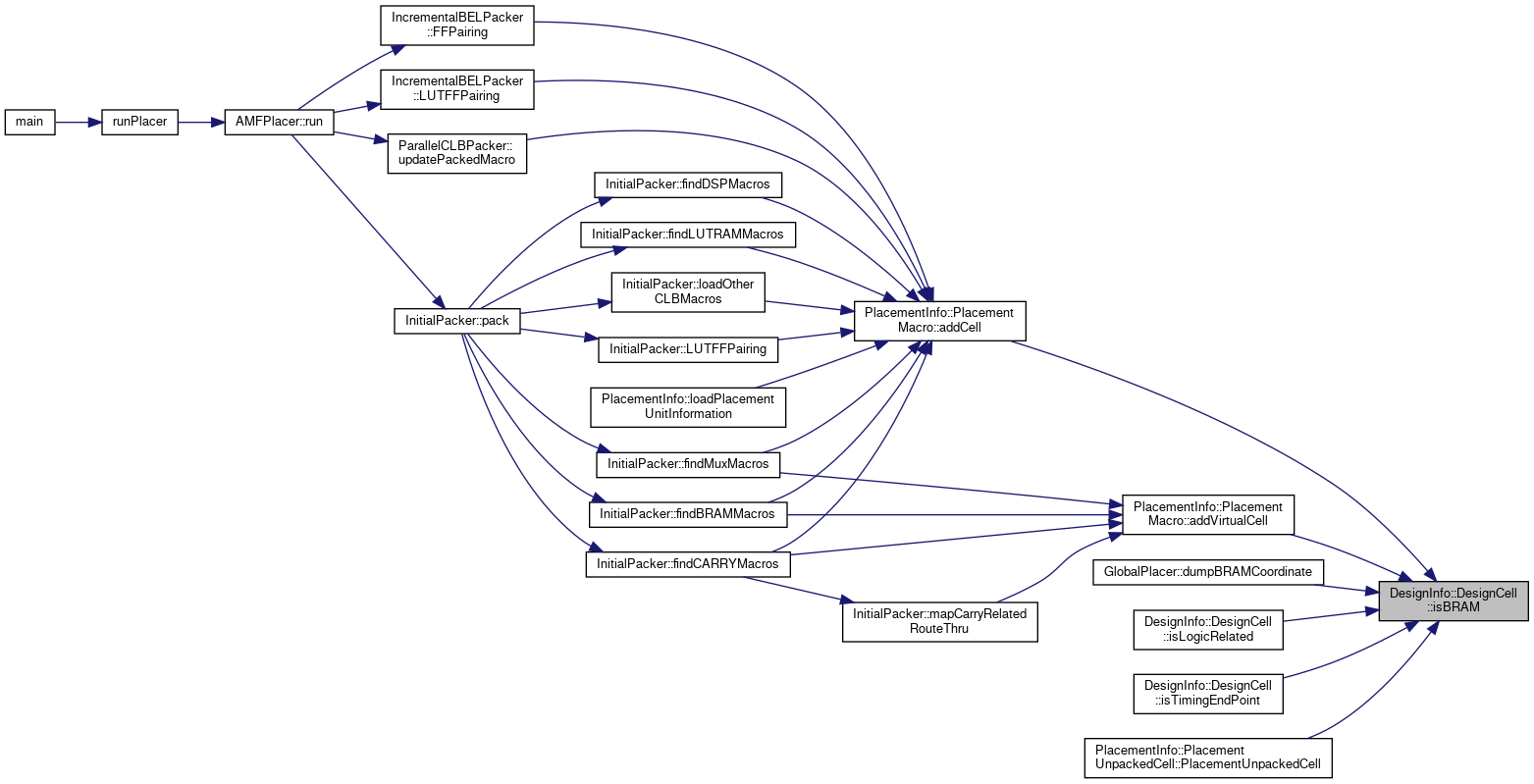

◆ isBRAM()

|

inline |

Definition at line 954 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), GlobalPlacer::dumpBRAMCoordinate(), isLogicRelated(), isTimingEndPoint(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

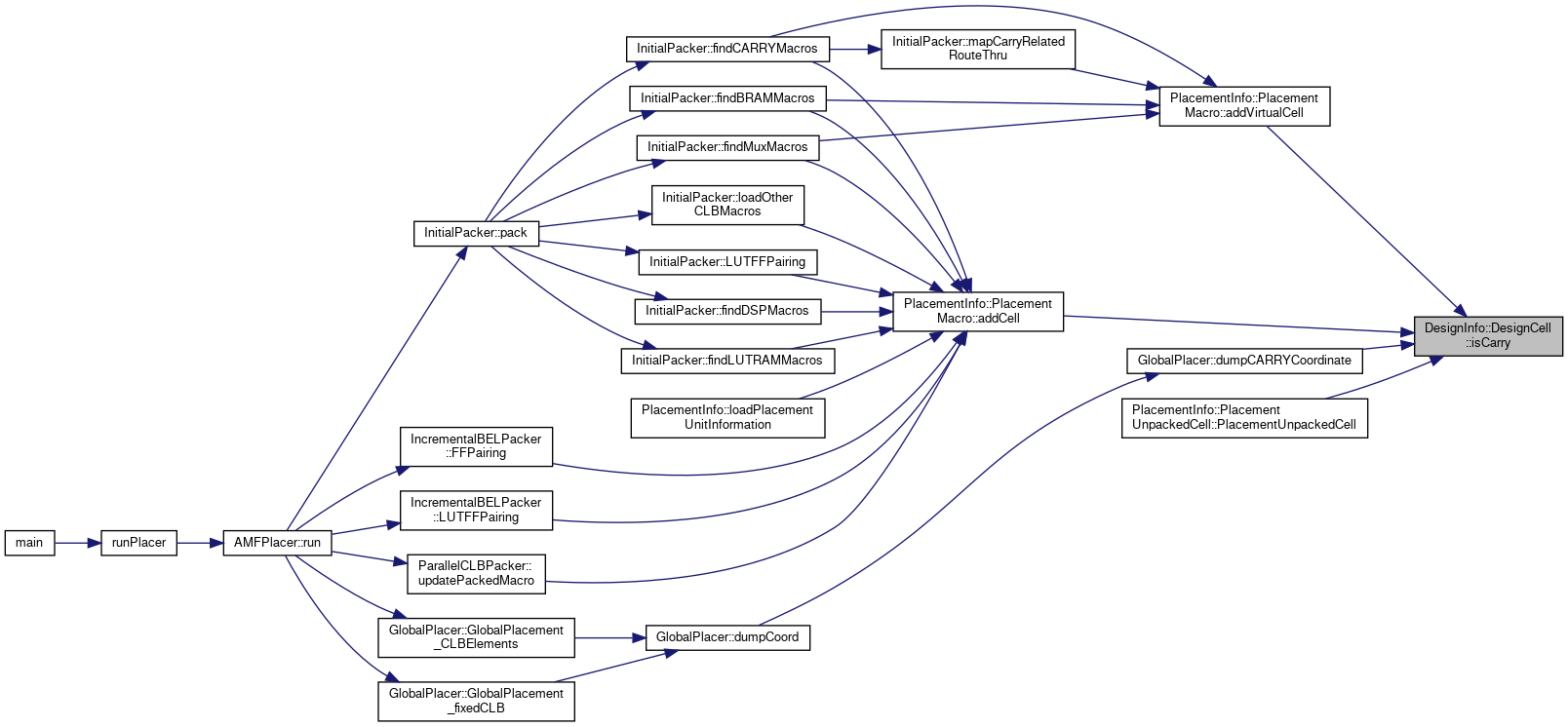

◆ isCarry()

|

inline |

Definition at line 963 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), GlobalPlacer::dumpCARRYCoordinate(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

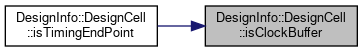

◆ isClockBuffer()

|

inline |

Definition at line 998 of file DesignInfo.h.

Referenced by isTimingEndPoint().

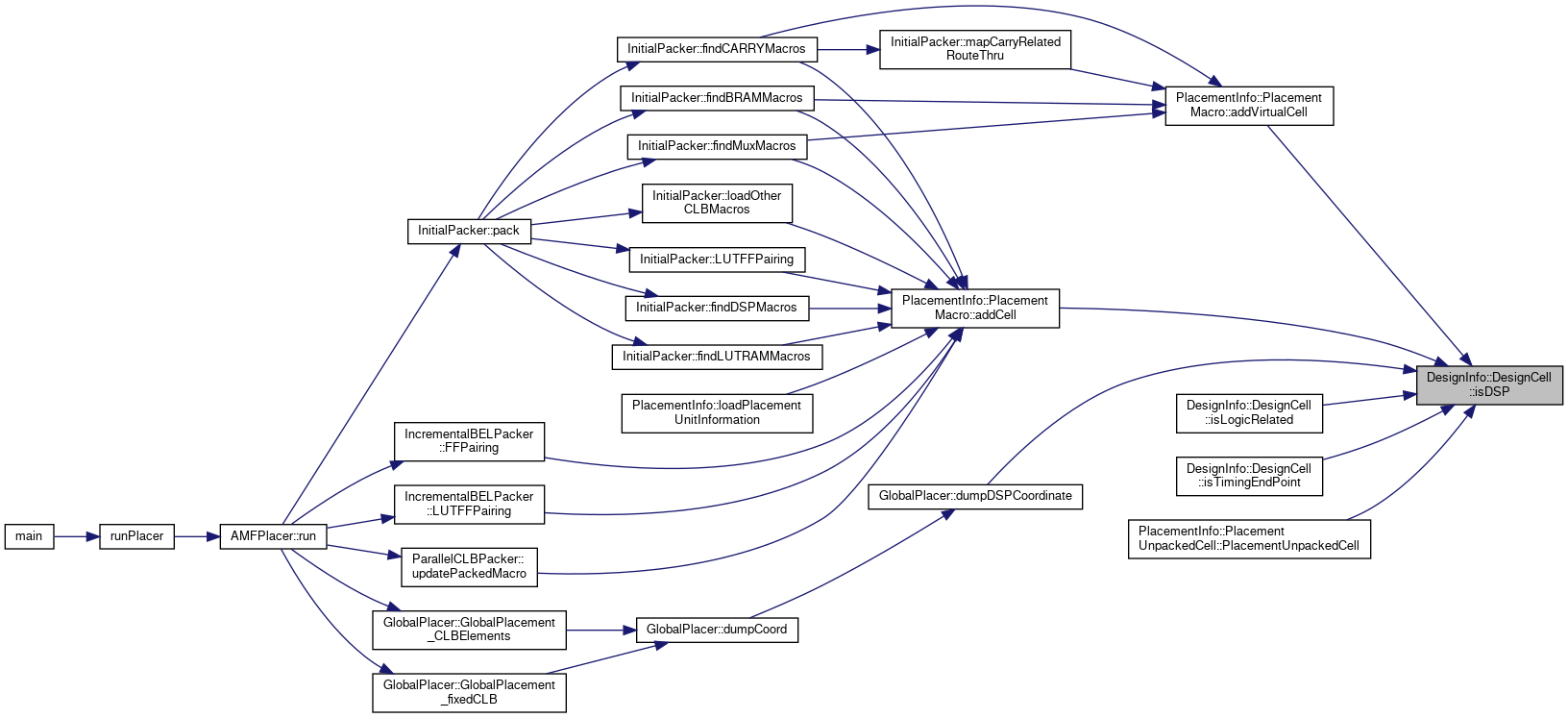

◆ isDSP()

|

inline |

Definition at line 971 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), GlobalPlacer::dumpDSPCoordinate(), isLogicRelated(), isTimingEndPoint(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

◆ isFF()

|

inline |

Definition at line 933 of file DesignInfo.h.

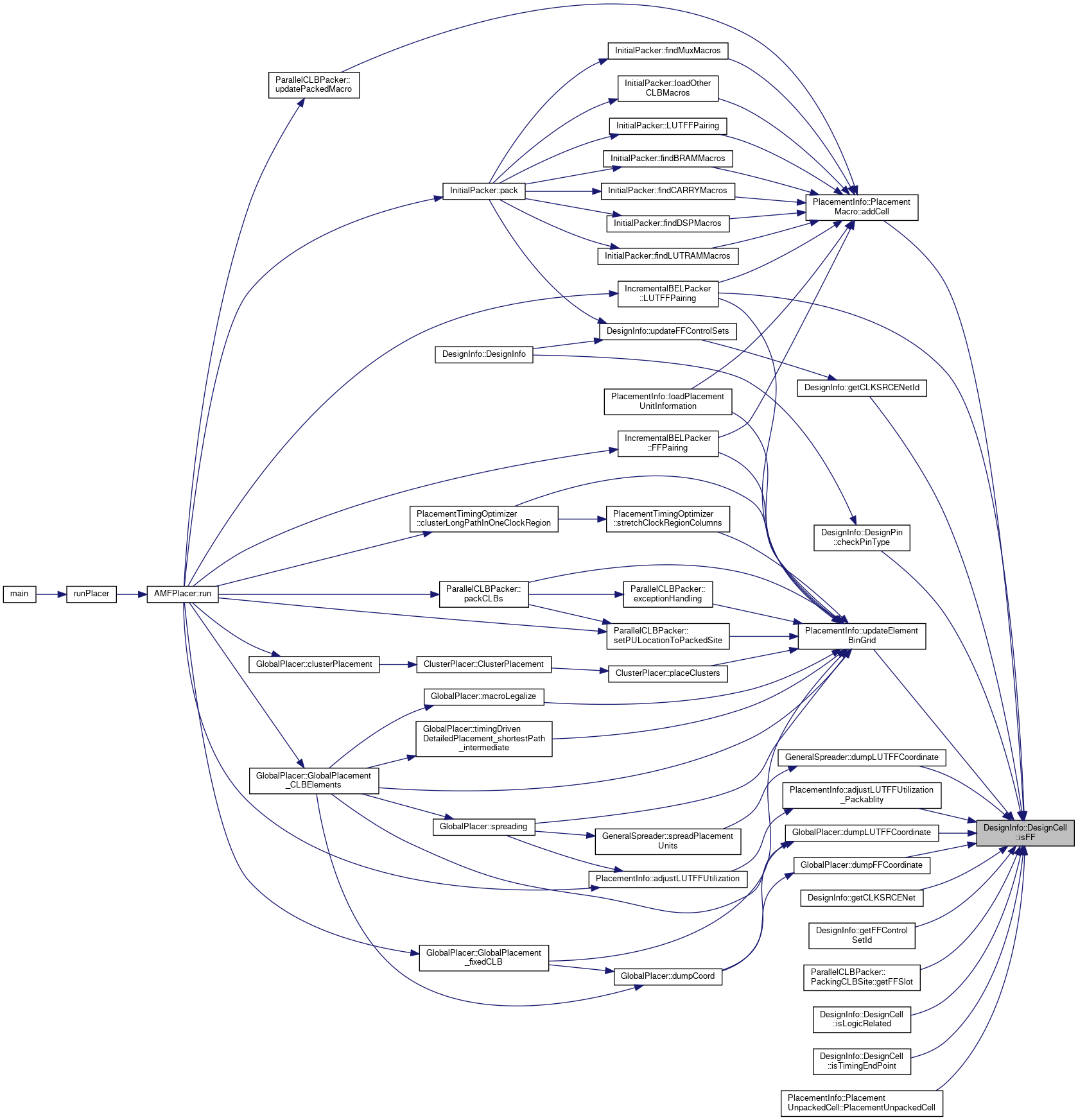

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::adjustLUTFFUtilization_Packablity(), DesignInfo::DesignPin::checkPinType(), GlobalPlacer::dumpFFCoordinate(), GeneralSpreader::dumpLUTFFCoordinate(), GlobalPlacer::dumpLUTFFCoordinate(), DesignInfo::getCLKSRCENet(), DesignInfo::getCLKSRCENetId(), DesignInfo::getFFControlSetId(), ParallelCLBPacker::PackingCLBSite::getFFSlot(), isLogicRelated(), isTimingEndPoint(), IncrementalBELPacker::LUTFFPairing(), PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell(), and PlacementInfo::updateElementBinGrid().

◆ isIO()

|

inline |

Definition at line 979 of file DesignInfo.h.

Referenced by isTimingEndPoint().

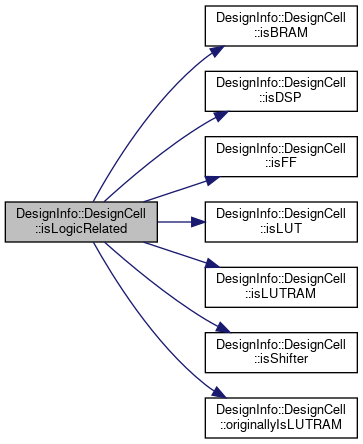

◆ isLogicRelated()

|

inline |

check whether the cell is related to logic computation

- Returns

- true

- false

Definition at line 1027 of file DesignInfo.h.

◆ isLUT()

|

inline |

Definition at line 927 of file DesignInfo.h.

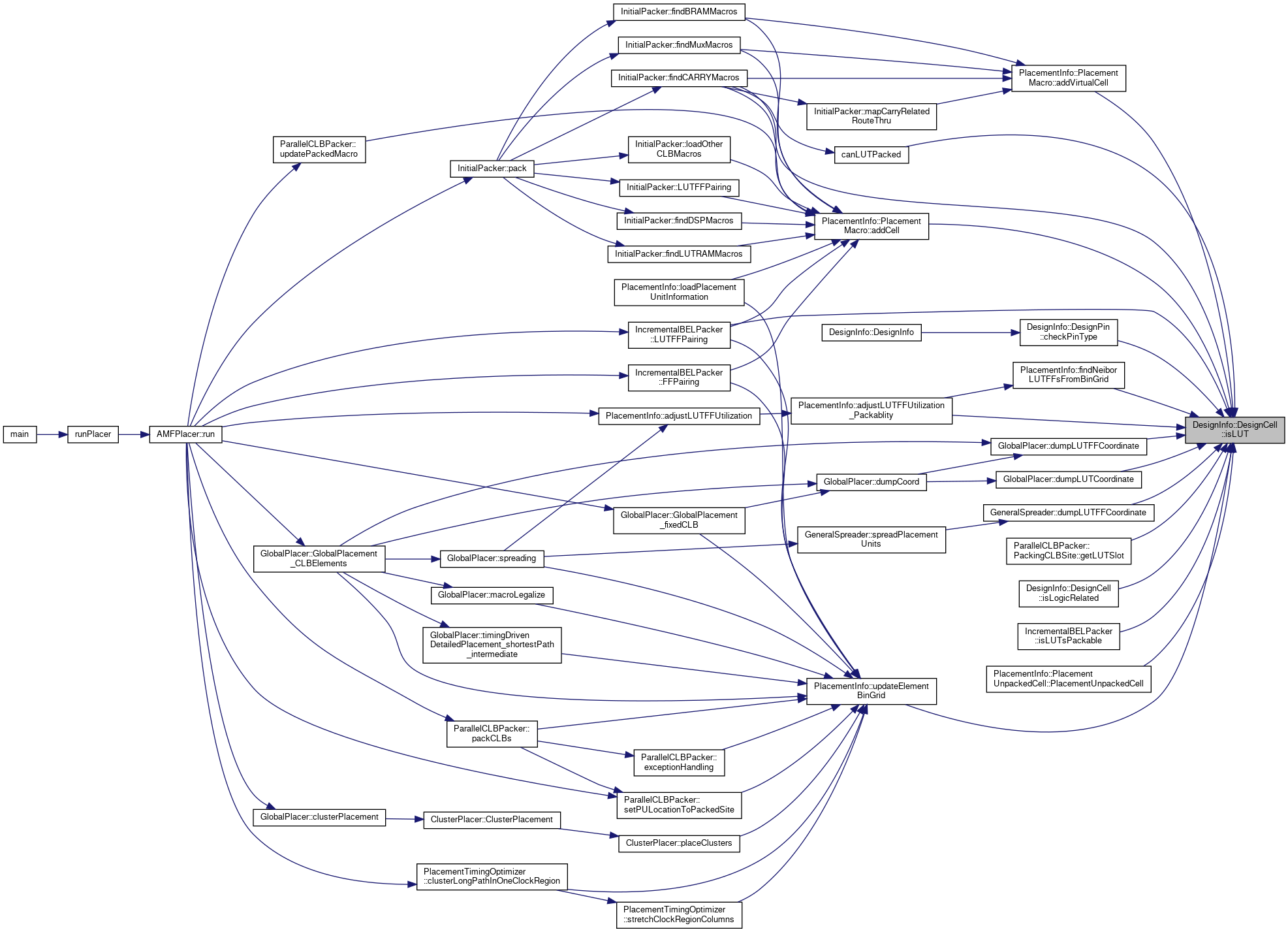

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), PlacementInfo::adjustLUTFFUtilization_Packablity(), canLUTPacked(), DesignInfo::DesignPin::checkPinType(), GlobalPlacer::dumpLUTCoordinate(), GeneralSpreader::dumpLUTFFCoordinate(), GlobalPlacer::dumpLUTFFCoordinate(), InitialPacker::findCARRYMacros(), PlacementInfo::findNeiborLUTFFsFromBinGrid(), ParallelCLBPacker::PackingCLBSite::getLUTSlot(), isLogicRelated(), IncrementalBELPacker::isLUTsPackable(), IncrementalBELPacker::LUTFFPairing(), PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell(), and PlacementInfo::updateElementBinGrid().

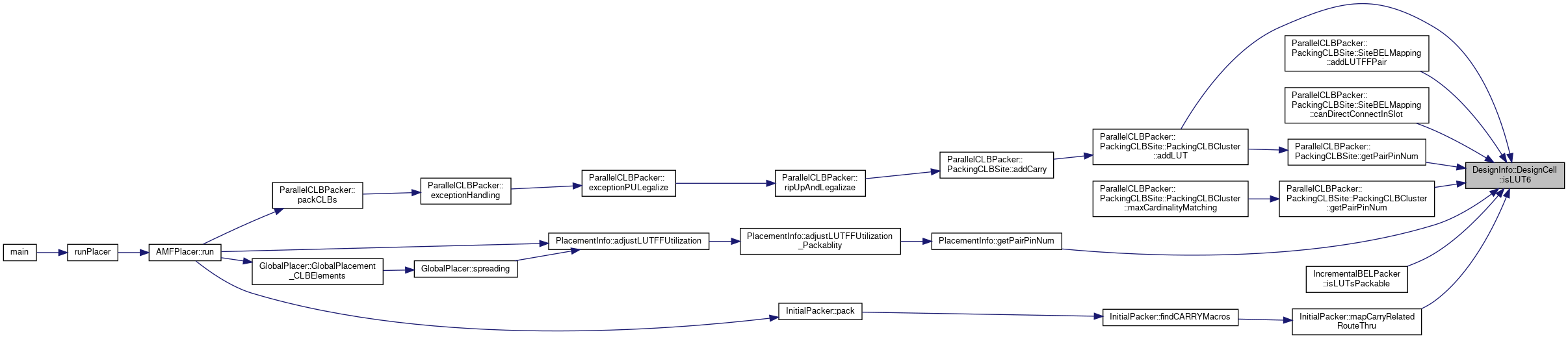

◆ isLUT6()

|

inline |

Definition at line 923 of file DesignInfo.h.

Referenced by ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addLUT(), ParallelCLBPacker::PackingCLBSite::SiteBELMapping::addLUTFFPair(), ParallelCLBPacker::PackingCLBSite::SiteBELMapping::canDirectConnectInSlot(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::getPairPinNum(), ParallelCLBPacker::PackingCLBSite::getPairPinNum(), PlacementInfo::getPairPinNum(), IncrementalBELPacker::isLUTsPackable(), and InitialPacker::mapCarryRelatedRouteThru().

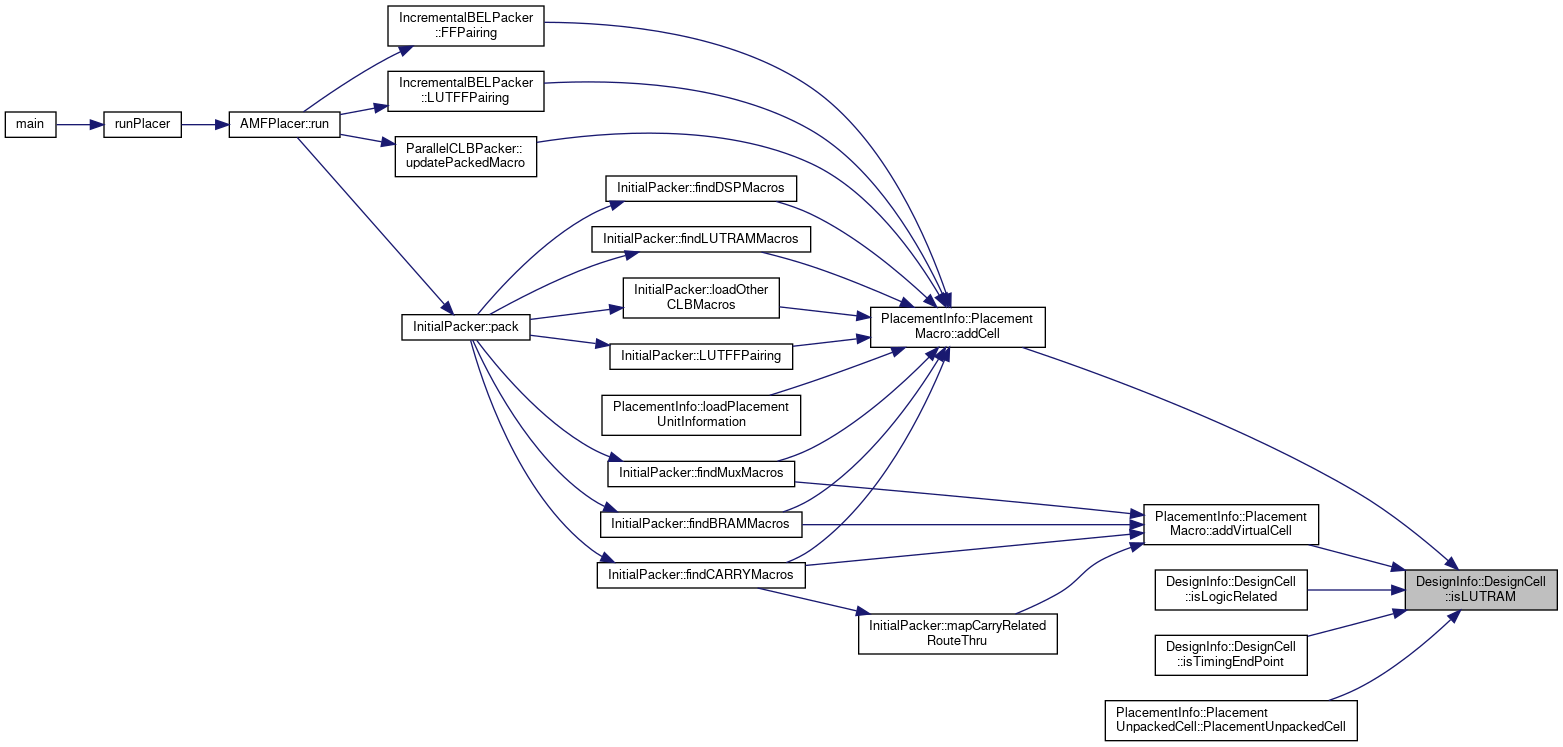

◆ isLUTRAM()

|

inline |

Definition at line 938 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), isLogicRelated(), isTimingEndPoint(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

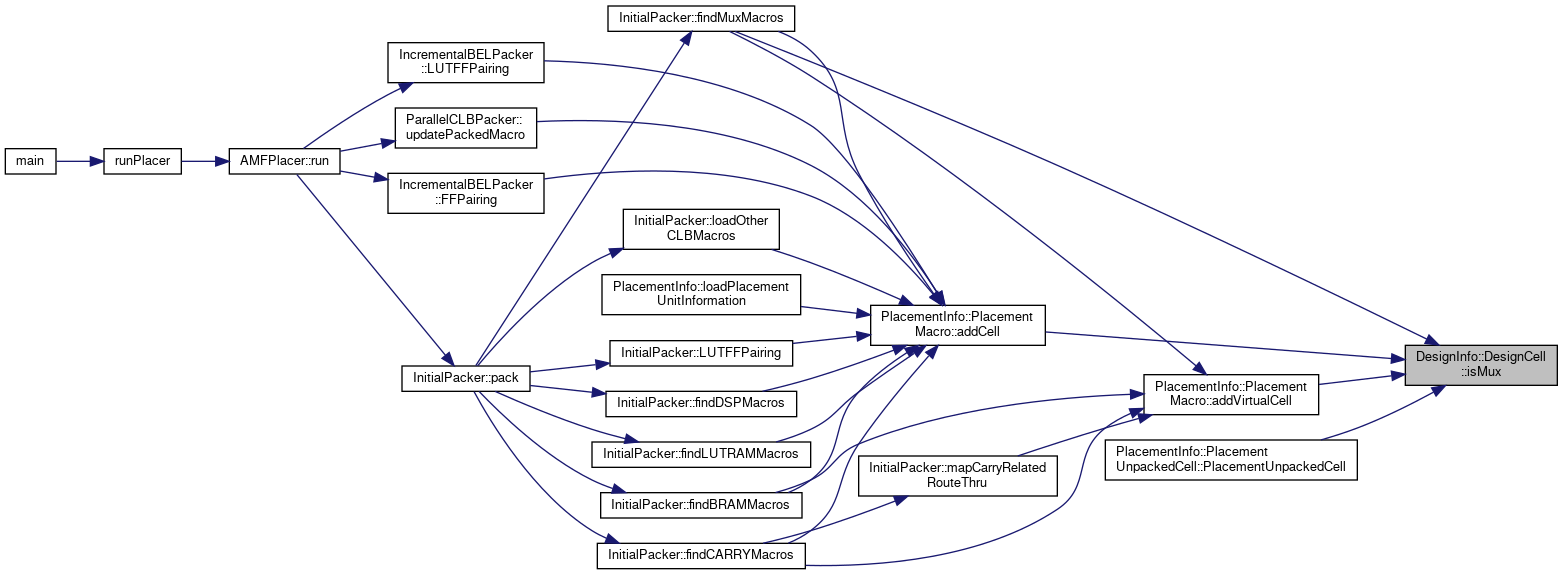

◆ isMux()

|

inline |

Definition at line 959 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), InitialPacker::findMuxMacros(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

◆ isShift()

|

inline |

Definition at line 967 of file DesignInfo.h.

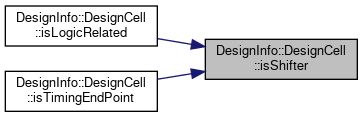

◆ isShifter()

|

inline |

Definition at line 1004 of file DesignInfo.h.

Referenced by isLogicRelated(), and isTimingEndPoint().

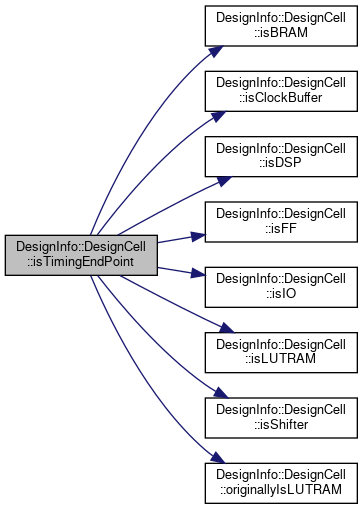

◆ isTimingEndPoint()

|

inline |

check whether the cell is an endpoint in timing graph

- Returns

- true

- false

Definition at line 1015 of file DesignInfo.h.

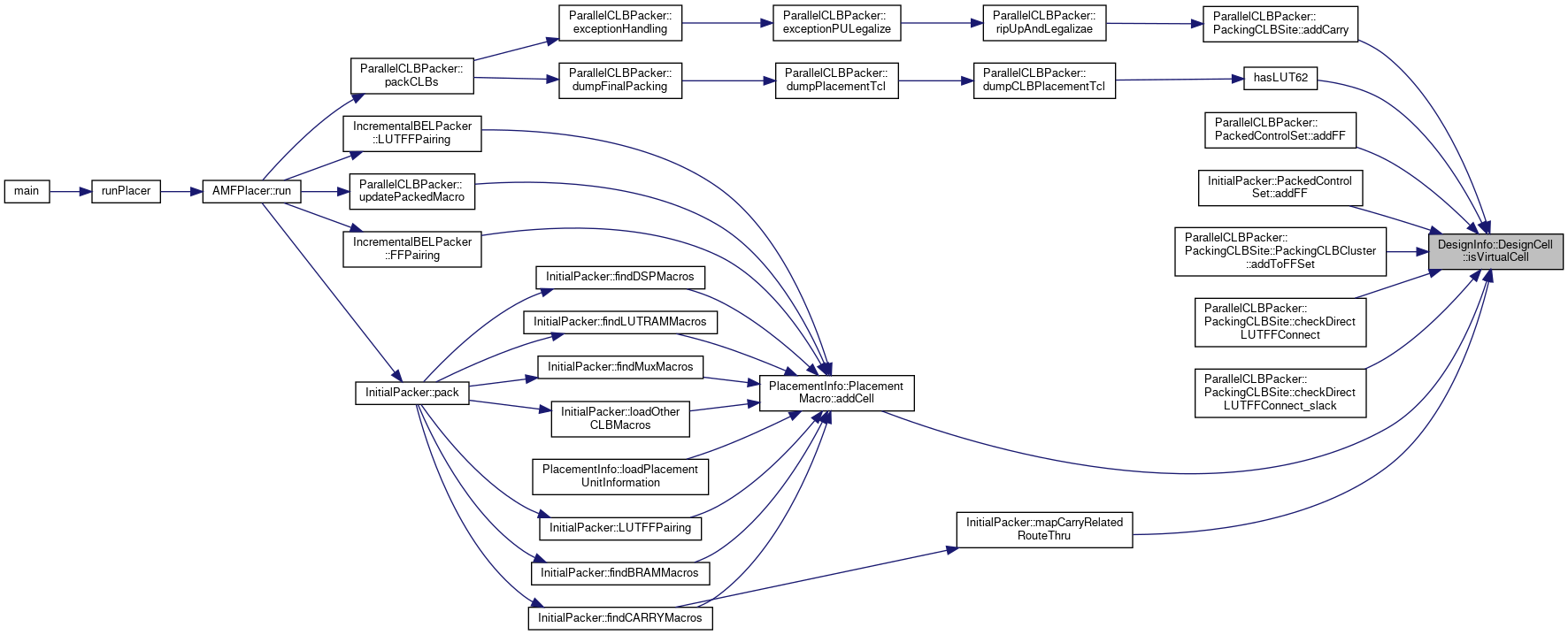

◆ isVirtualCell()

|

inline |

Definition at line 1042 of file DesignInfo.h.

Referenced by ParallelCLBPacker::PackingCLBSite::addCarry(), PlacementInfo::PlacementMacro::addCell(), ParallelCLBPacker::PackedControlSet::addFF(), InitialPacker::PackedControlSet::addFF(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addToFFSet(), ParallelCLBPacker::PackingCLBSite::checkDirectLUTFFConnect(), ParallelCLBPacker::PackingCLBSite::checkDirectLUTFFConnect_slack(), hasLUT62(), and InitialPacker::mapCarryRelatedRouteThru().

◆ originallyIsLUTRAM()

|

inline |

Definition at line 945 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell(), PlacementInfo::PlacementMacro::addVirtualCell(), isLogicRelated(), isTimingEndPoint(), and PlacementInfo::PlacementUnpackedCell::PlacementUnpackedCell().

◆ setControlSetInfo()

|

inline |

Set the Control Set Info object of this cell.

A control set is a combination of CLK, CE and SR signal. It could be nullptr (not related to control set)

- Parameters

-

_controlSetInfo

Definition at line 1066 of file DesignInfo.h.

◆ setHasDSPReg()

|

inline |

Definition at line 1114 of file DesignInfo.h.

◆ setTimingLength()

|

inline |

Definition at line 1119 of file DesignInfo.h.

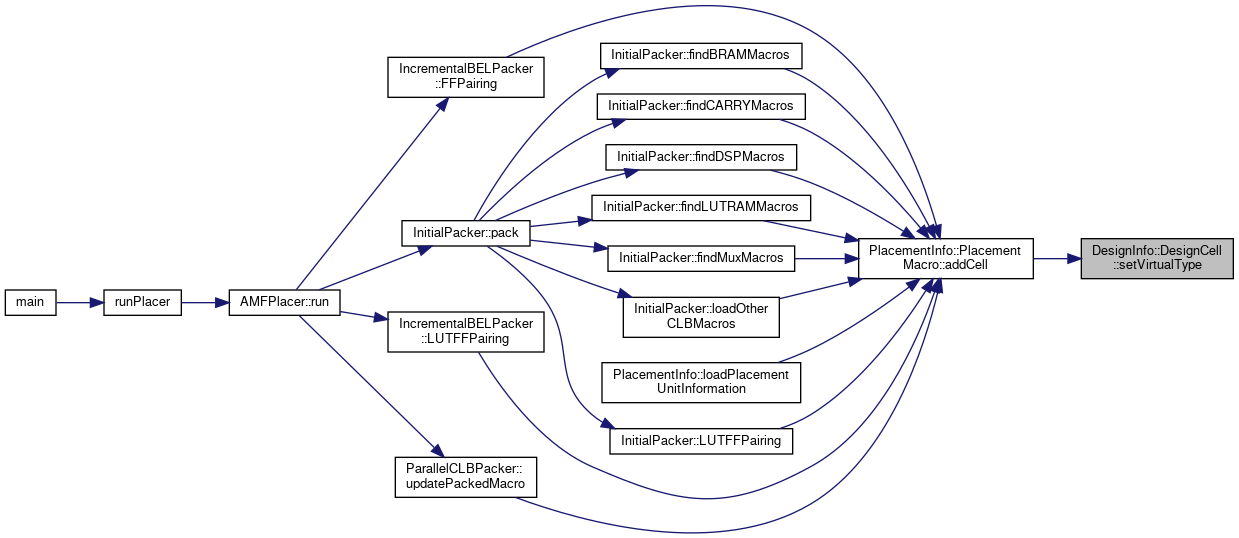

◆ setVirtualType()

|

inline |

Set the Virtual Type object which might override the actual type in later processing.

for example, for some LUT1-5, we might set its virtual type to be LUT6 to ensure that it will be paired with other LUTs.

- Parameters

-

NewCellType

Definition at line 1079 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addCell().

Member Data Documentation

◆ cellType

|

private |

Definition at line 1139 of file DesignInfo.h.

Referenced by DesignCell(), getCellType(), isBRAM(), isCarry(), isClockBuffer(), isDSP(), isFF(), isIO(), isLUT(), isLUT6(), isLUTRAM(), isMux(), isShift(), isShifter(), and setVirtualType().

◆ clockNetPtrs

|

private |

Definition at line 1137 of file DesignInfo.h.

Referenced by addClockNet(), and getClockNets().

◆ controlSetInfo

|

private |

Definition at line 1143 of file DesignInfo.h.

Referenced by getControlSetInfo(), and setControlSetInfo().

◆ hasDSPReg

|

private |

Definition at line 1142 of file DesignInfo.h.

Referenced by checkHasDSPReg(), and setHasDSPReg().

◆ inputNetPtrs

|

private |

Definition at line 1135 of file DesignInfo.h.

Referenced by DesignCell(), and getInputNets().

◆ inputPinPtrs

|

private |

Definition at line 1131 of file DesignInfo.h.

Referenced by DesignCell(), and getInputPins().

◆ isVirtual

|

private |

Definition at line 1141 of file DesignInfo.h.

Referenced by DesignCell(), and isVirtualCell().

◆ netNames

|

private |

Definition at line 1138 of file DesignInfo.h.

Referenced by DesignCell().

◆ netPtrs

|

private |

Definition at line 1134 of file DesignInfo.h.

Referenced by DesignCell().

◆ oriCellType

|

private |

Definition at line 1140 of file DesignInfo.h.

Referenced by DesignCell(), getOriCellType(), and originallyIsLUTRAM().

◆ outputNetPtrs

|

private |

Definition at line 1136 of file DesignInfo.h.

Referenced by DesignCell(), and getOutputNets().

◆ outputPinPtrs

|

private |

Definition at line 1132 of file DesignInfo.h.

Referenced by DesignCell(), and getOutputPins().

◆ pinNames

|

private |

Definition at line 1133 of file DesignInfo.h.

Referenced by DesignCell().

◆ pinPtrs

|

private |

Definition at line 1130 of file DesignInfo.h.

Referenced by DesignCell(), getPins(), and ~DesignCell().

◆ timingLength

|

private |

Definition at line 1144 of file DesignInfo.h.

Referenced by getTimingLength(), and setTimingLength().

The documentation for this class was generated from the following files:

- src/lib/HiFPlacer/designInfo/DesignInfo.h

- src/lib/HiFPlacer/designInfo/DesignInfo.cc