Information related to FPGA designs, including design cells and their interconnections. More...

#include <DesignInfo.h>

Classes | |

| class | ControlSetInfo |

| A control set is a combination of CLK, CE and SR signal. It could be nullptr (not related to control set) More... | |

| class | DesignCell |

| a DesignCell in design netlist, DesignPin objects of which might connect to DesignNet objects More... | |

| class | DesignElement |

| basic class of element in a design. More... | |

| class | DesignNet |

| a design net (hyperedge) defined in the design, connecting to pins of cells More... | |

| class | DesignPin |

| A design pin on a design cell connected to a net. More... | |

Public Member Functions | |

| bool | isClockBuffer (DesignCellType cellType) |

| bool | isShifter (DesignCellType cellType) |

| bool | isLogicRelated (DesignCellType cellType) |

| check whether the cell is related to logic computation More... | |

| DesignInfo (std::map< std::string, std::string > &JSONCfg, DeviceInfo *deviceInfo) | |

| Construct a new Design Info object based on user-defined settings and device information. More... | |

| ~DesignInfo () | |

| void | addPinToNet (DesignPin *curPin) |

| bind a pin to an existing net. If the net does not exist, new one. More... | |

| DesignCellType | fromStringToCellType (std::string &cellName, std::string &typeName) |

| translate a string into a DesignCellType for a cell More... | |

| DesignCell * | addCell (DesignCell *curCell) |

| add a cell into the design information More... | |

| void | getCLKSRCENetId (DesignInfo::DesignCell *curFF, int &CLKId, int &SRId, int &CEId) |

| extract the ids of CLK, SR, and CE for a given FF More... | |

| void | getCLKSRCENet (DesignInfo::DesignCell *curFF, DesignNet **CLK, DesignNet **SR, DesignNet **CE) |

| extract the pointers of CLK, SR, and CE for a given FF More... | |

| void | loadClocks (std::string clockFileName) |

| load the global clock signals from a design information file More... | |

| void | updateFFControlSets () |

| go through the FF cells to extract control sets for later processing More... | |

| void | enhanceFFControlSetNets () |

| intend to enhance the nets between FFs in a control set to make later packing easier More... | |

| std::vector< ControlSetInfo * > & | getControlSets () |

| Get the control sets in the design. More... | |

| int | getFFControlSetId (DesignCell *curFF) |

| get the id of the control set of a given FF More... | |

| void | loadUserDefinedClusterNets () |

| for user-defined-cluster-based optimization, load the nets in a user-defined cluster for later processing More... | |

| int | getNumCells () |

| int | getNumNets () |

| std::vector< DesignCell * > & | getCells () |

| std::vector< DesignNet * > & | getNets () |

| std::vector< DesignPin * > & | getPins () |

| void | resetNetEnhanceRatio () |

| disable enhancement of all the nets in the design (reset extra weight to be 1) More... | |

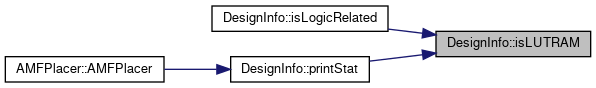

| void | printStat (bool verbose=false) |

| DesignCell * | getCell (std::string &tmpName) |

| DesignNet * | getNet (std::string &tmpName) |

| std::vector< std::vector< DesignCell * > > & | getPredefinedClusters () |

| Get the predefined clusters which are defined in design configuration files. More... | |

| std::map< DesignCellType, std::vector< DesignCell * > > & | getType2Cells () |

| void | resetLUTFFDeterminedOccupation () |

| reset the LUTFFDeterminedOccupation object More... | |

| int | getDeterminedOccupation (int cellId) |

| void | setDeterminedOccupation (int cellId, int occupation) |

| Set the Determined Occupation of a specific cell. More... | |

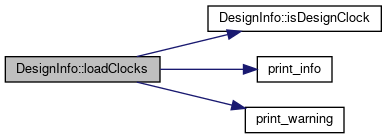

| bool | isDesignClock (DesignNet *tmpNet) |

| check if a net is a global clock indicated by input design files More... | |

| std::vector< DesignNet * > & | getClocksInDesign () |

| Get the all the clock nets in the design. More... | |

| std::set< DesignCell * > & | getCellsUnderClock (DesignNet *clock) |

| Get the cells driven by a given clock net. More... | |

Static Public Member Functions | |

| static bool | FFSRCompatible (DesignCellType typeA, DesignCellType typeB) |

| static bool | getFFSRType (DesignCellType typeA) |

| static bool | isLUT (DesignCellType cellType) |

| static bool | isCarry (DesignCellType cellType) |

| static bool | isDSP (DesignCellType cellType) |

| static bool | isBRAM (DesignCellType cellType) |

| static bool | isMux (DesignCellType cellType) |

| static bool | isLUTRAM (DesignCellType cellType) |

| static bool | isFF (DesignCellType cellType) |

| static bool | isIO (DesignCellType cellType) |

Public Attributes | |

| std::vector< std::string > | DesignCellTypeStr {CELLTYPESTRS} |

Private Attributes | |

| std::vector< DesignNet * > | netlist |

| std::vector< DesignCell * > | cells |

| std::vector< DesignPin * > | pins |

| std::map< std::string, DesignNet * > | name2Net |

| std::map< std::string, int > | aliasNet2AliasNetId |

| std::map< std::string, DesignCell * > | name2Cell |

| std::vector< std::vector< DesignCell * > > | predefinedClusters |

| the predefined clusters which are defined in design configuration files More... | |

| std::map< DesignCellType, std::vector< DesignCell * > > | type2Cells |

| std::set< std::pair< DesignPin *, DesignPin * > > | connectedPinsWithSmallNet |

| connected pin pairs by nets with a small number of pins More... | |

| std::vector< int > | LUTFFDeterminedOccupation |

| LUTFFDeterminedOccupation is used to record the final resource demand of a LUT/FF after final packing. More... | |

| std::map< std::tuple< int, int, int, int >, int > | CLKSRCEFFType2ControlSetInfoId |

| the mapping from the tuple of CLK/SR/CE ids and FF type to a unique defined control set id More... | |

| std::vector< int > | FFId2ControlSetId |

| the mapping from FF IDs to a unique defined control set id More... | |

| std::vector< ControlSetInfo * > | controlSets |

| std::vector< DesignNet * > | clocks |

| std::set< DesignNet * > | clockSet |

| std::map< DesignNet *, std::set< DesignCell * > > | clock2Cells |

| the mapping from clocks to their corresponding cells driven by the clock net More... | |

| std::map< std::string, std::string > & | JSONCfg |

| std::string | designArchievedTextFileName |

Detailed Description

Information related to FPGA designs, including design cells and their interconnections.

Definition at line 50 of file DesignInfo.h.

Member Enumeration Documentation

◆ DesignCellType

design cell types

This is a design concept. These cell types should be mapped to device BEL types (resour concept).

Definition at line 72 of file DesignInfo.h.

◆ DesignElementType

types of the elements in a design

There are cells in a design, pins of which are interconnected via nets.

| Enumerator | |

|---|---|

| ElementType_cell | |

| ElementType_pin | |

| ElementType_net | |

| ElementType_graph | |

Definition at line 58 of file DesignInfo.h.

◆ DesignPinType

| Enumerator | |

|---|---|

| PinType_LUTInput | |

| PinType_LUTOutput | |

| PinType_CLK | |

| PinType_Q | |

| PinType_D | |

| PinType_E | |

| PinType_SR | |

| PinType_Others | |

Definition at line 196 of file DesignInfo.h.

Constructor & Destructor Documentation

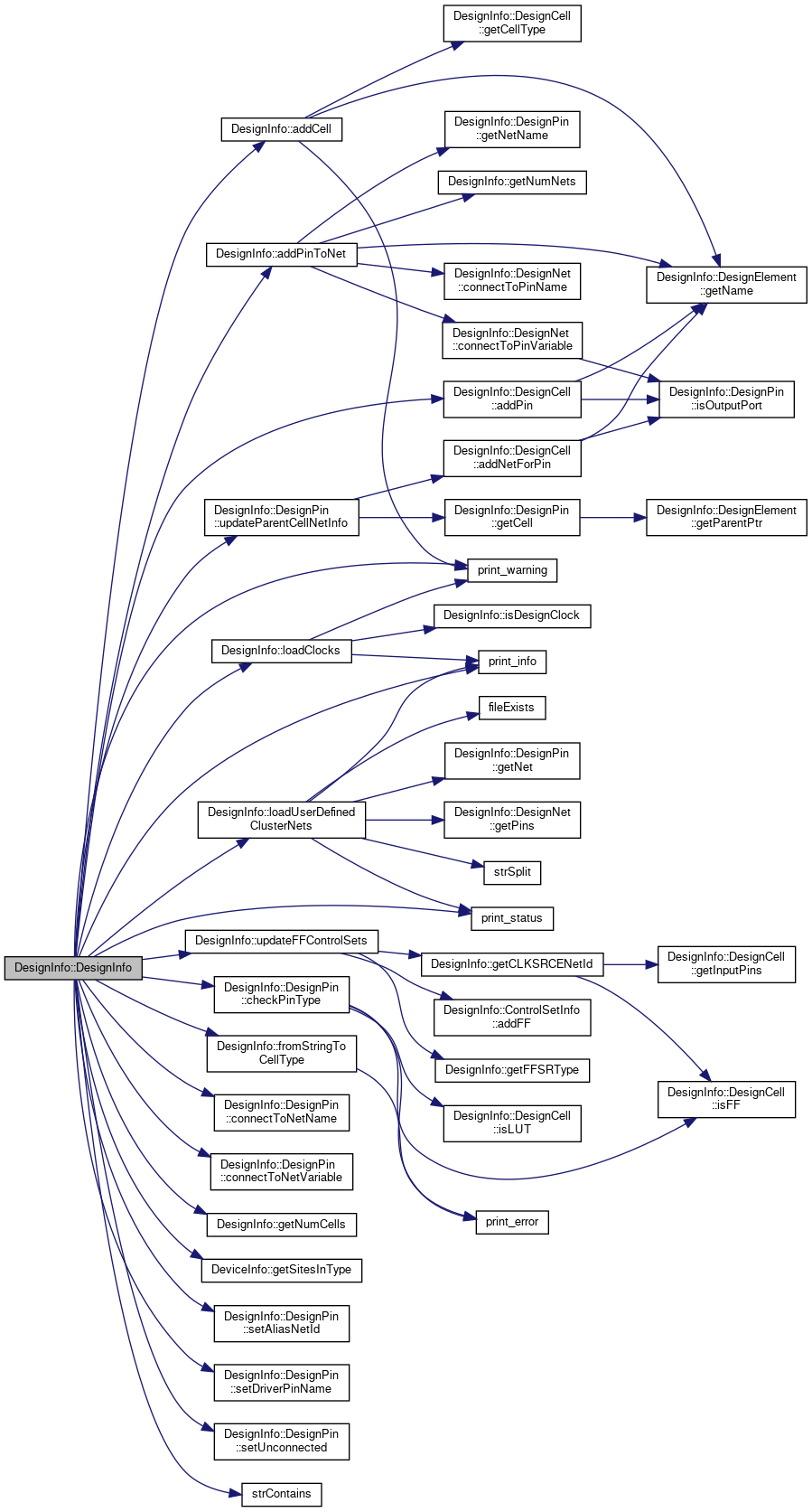

◆ DesignInfo()

| DesignInfo::DesignInfo | ( | std::map< std::string, std::string > & | JSONCfg, |

| DeviceInfo * | deviceInfo | ||

| ) |

Construct a new Design Info object based on user-defined settings and device information.

- Parameters

-

JSONCfg the file of user-defined settings deviceInfo device information

The design information file will contain information like the text shown below

Definition at line 144 of file DesignInfo.cc.

◆ ~DesignInfo()

|

inline |

Definition at line 1433 of file DesignInfo.h.

Member Function Documentation

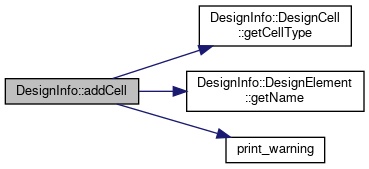

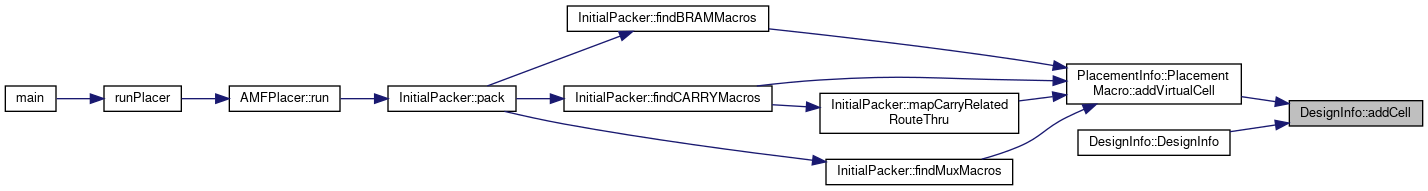

◆ addCell()

| DesignInfo::DesignCell * DesignInfo::addCell | ( | DesignCell * | curCell | ) |

add a cell into the design information

- Parameters

-

curCell target cell

- Returns

- DesignCell* if there is duplicated object, delete the new cell and return the existing object

Definition at line 617 of file DesignInfo.cc.

Referenced by PlacementInfo::PlacementMacro::addVirtualCell(), and DesignInfo().

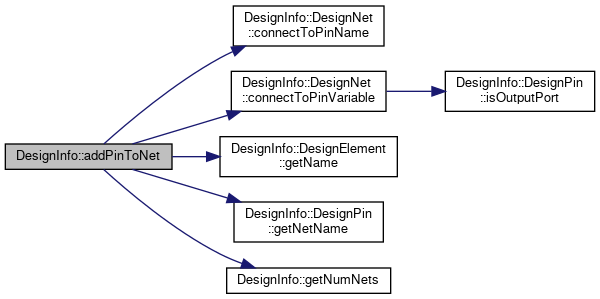

◆ addPinToNet()

| void DesignInfo::addPinToNet | ( | DesignPin * | curPin | ) |

bind a pin to an existing net. If the net does not exist, new one.

- Parameters

-

curPin target pin

Definition at line 130 of file DesignInfo.cc.

Referenced by DesignInfo().

◆ enhanceFFControlSetNets()

| void DesignInfo::enhanceFFControlSetNets | ( | ) |

intend to enhance the nets between FFs in a control set to make later packing easier

Definition at line 464 of file DesignInfo.cc.

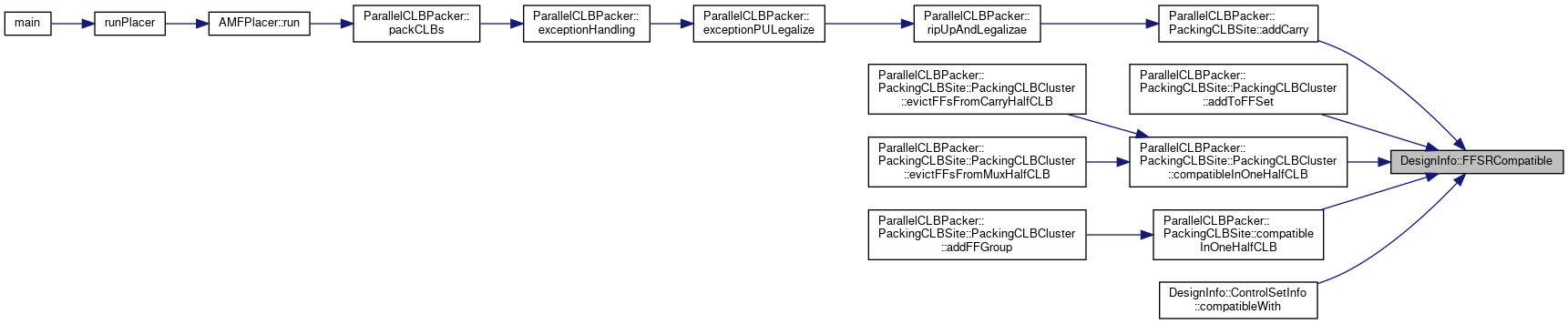

◆ FFSRCompatible()

|

inlinestatic |

Definition at line 148 of file DesignInfo.h.

Referenced by ParallelCLBPacker::PackingCLBSite::addCarry(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::addToFFSet(), ParallelCLBPacker::PackingCLBSite::PackingCLBCluster::compatibleInOneHalfCLB(), ParallelCLBPacker::PackingCLBSite::compatibleInOneHalfCLB(), and DesignInfo::ControlSetInfo::compatibleWith().

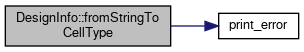

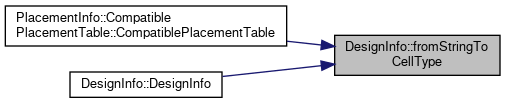

◆ fromStringToCellType()

| DesignInfo::DesignCellType DesignInfo::fromStringToCellType | ( | std::string & | cellName, |

| std::string & | typeName | ||

| ) |

translate a string into a DesignCellType for a cell

- Parameters

-

cellName target cell typeName type name string

- Returns

- DesignCellType

Definition at line 606 of file DesignInfo.cc.

Referenced by PlacementInfo::CompatiblePlacementTable::CompatiblePlacementTable(), and DesignInfo().

◆ getCell()

|

inline |

Definition at line 1634 of file DesignInfo.h.

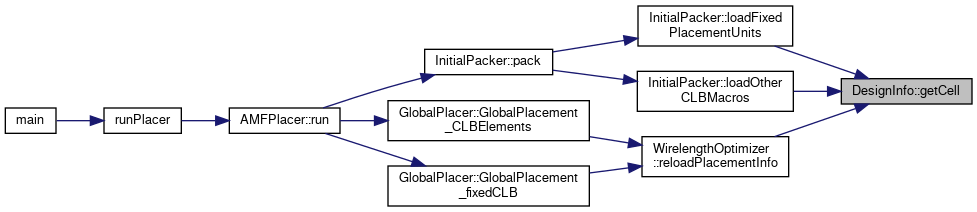

Referenced by InitialPacker::loadFixedPlacementUnits(), InitialPacker::loadOtherCLBMacros(), and WirelengthOptimizer::reloadPlacementInfo().

◆ getCells()

|

inline |

Definition at line 1609 of file DesignInfo.h.

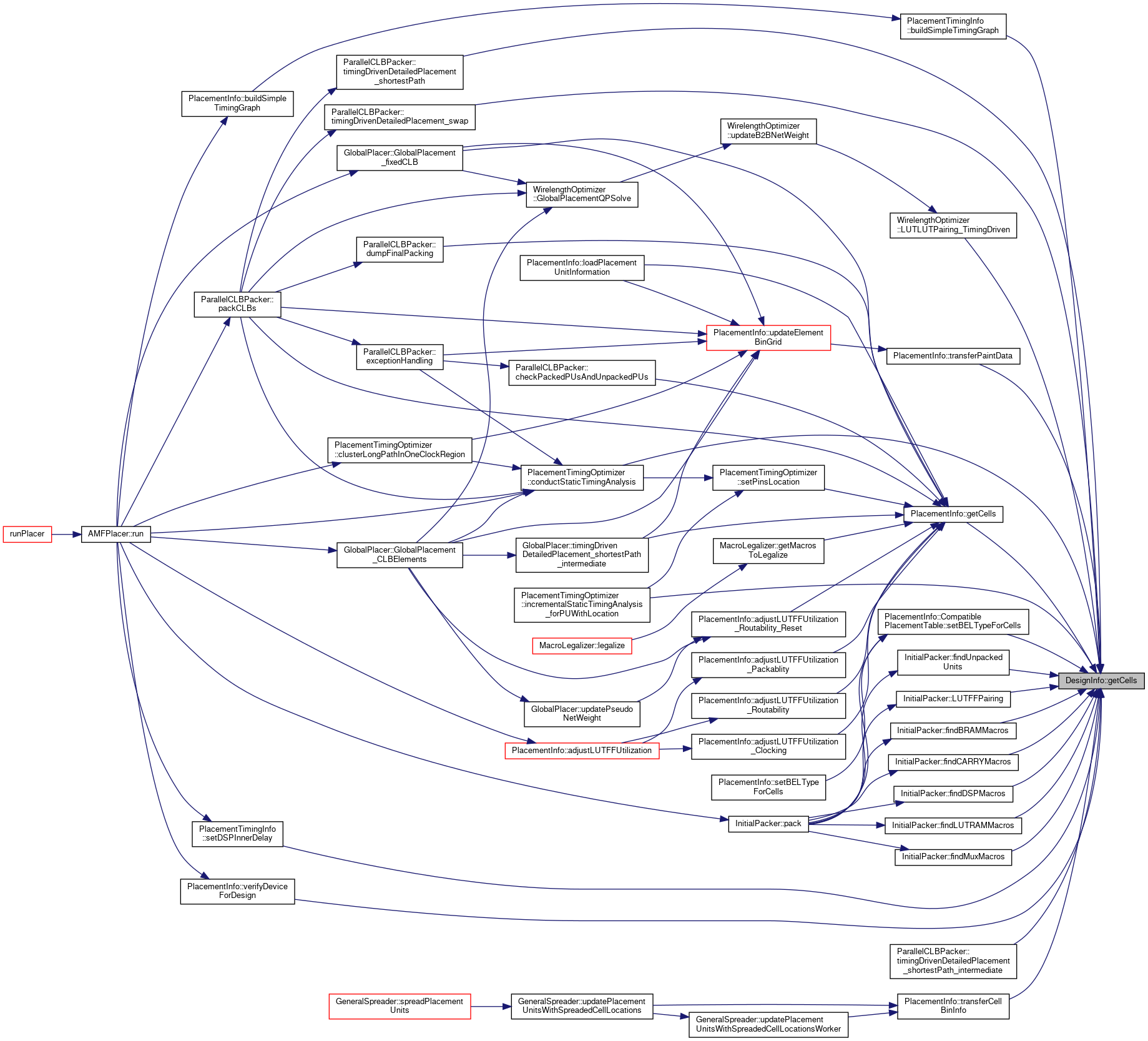

Referenced by PlacementTimingInfo::buildSimpleTimingGraph(), PlacementTimingOptimizer::conductStaticTimingAnalysis(), InitialPacker::findBRAMMacros(), InitialPacker::findCARRYMacros(), InitialPacker::findDSPMacros(), InitialPacker::findLUTRAMMacros(), InitialPacker::findMuxMacros(), InitialPacker::findUnpackedUnits(), PlacementInfo::getCells(), PlacementTimingOptimizer::incrementalStaticTimingAnalysis_forPUWithLocation(), InitialPacker::LUTFFPairing(), WirelengthOptimizer::LUTLUTPairing_TimingDriven(), PlacementInfo::CompatiblePlacementTable::setBELTypeForCells(), PlacementTimingInfo::setDSPInnerDelay(), ParallelCLBPacker::timingDrivenDetailedPlacement_shortestPath(), ParallelCLBPacker::timingDrivenDetailedPlacement_shortestPath_intermediate(), ParallelCLBPacker::timingDrivenDetailedPlacement_swap(), PlacementInfo::transferCellBinInfo(), PlacementInfo::transferPaintData(), and PlacementInfo::verifyDeviceForDesign().

◆ getCellsUnderClock()

|

inline |

Get the cells driven by a given clock net.

- Parameters

-

clock a clock net

- Returns

- std::set<DesignCell *>&

Definition at line 1734 of file DesignInfo.h.

Referenced by ClusterPlacer::createClockBasedClusterUnits().

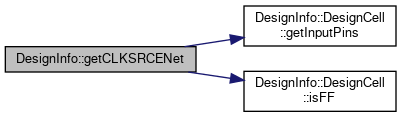

◆ getCLKSRCENet()

|

inline |

extract the pointers of CLK, SR, and CE for a given FF

- Parameters

-

curFF a given FF CLK output CLK pointer SR output SR pointer CE output CE pointer

Definition at line 1517 of file DesignInfo.h.

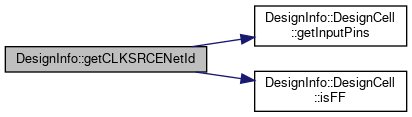

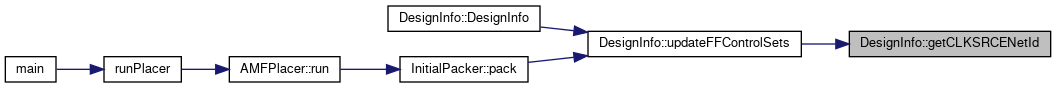

◆ getCLKSRCENetId()

|

inline |

extract the ids of CLK, SR, and CE for a given FF

- Parameters

-

curFF a given FF CLKId output CLK Id SRId output SR Id CEId output CE Id

Definition at line 1475 of file DesignInfo.h.

Referenced by updateFFControlSets().

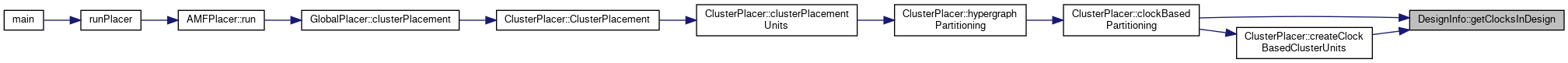

◆ getClocksInDesign()

|

inline |

Get the all the clock nets in the design.

- Returns

- std::vector<DesignNet *>&

Definition at line 1723 of file DesignInfo.h.

Referenced by ClusterPlacer::clockBasedPartitioning(), and ClusterPlacer::createClockBasedClusterUnits().

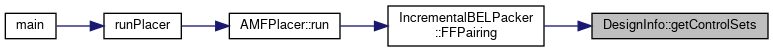

◆ getControlSets()

|

inline |

Get the control sets in the design.

- Returns

- std::vector<ControlSetInfo *>&

Definition at line 1575 of file DesignInfo.h.

Referenced by IncrementalBELPacker::FFPairing().

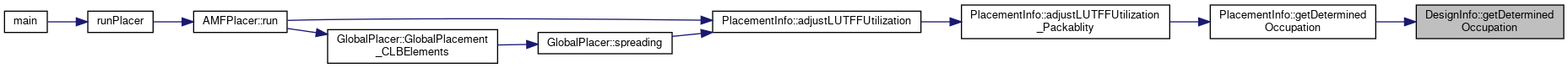

◆ getDeterminedOccupation()

|

inline |

@briefget the Determined Occupation of a specific cell

LUTFFDeterminedOccupation is used to record the final resource demand of a LUT/FF after final packing

- Parameters

-

cellId target cell

- Returns

- int

Definition at line 1688 of file DesignInfo.h.

Referenced by PlacementInfo::getDeterminedOccupation().

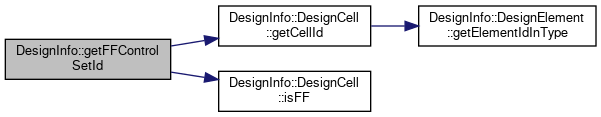

◆ getFFControlSetId()

|

inline |

get the id of the control set of a given FF

- Parameters

-

curFF target FF

- Returns

- int

Definition at line 1586 of file DesignInfo.h.

◆ getFFSRType()

|

inlinestatic |

Definition at line 179 of file DesignInfo.h.

Referenced by updateFFControlSets().

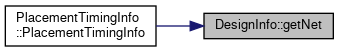

◆ getNet()

|

inline |

Definition at line 1644 of file DesignInfo.h.

Referenced by PlacementTimingInfo::PlacementTimingInfo().

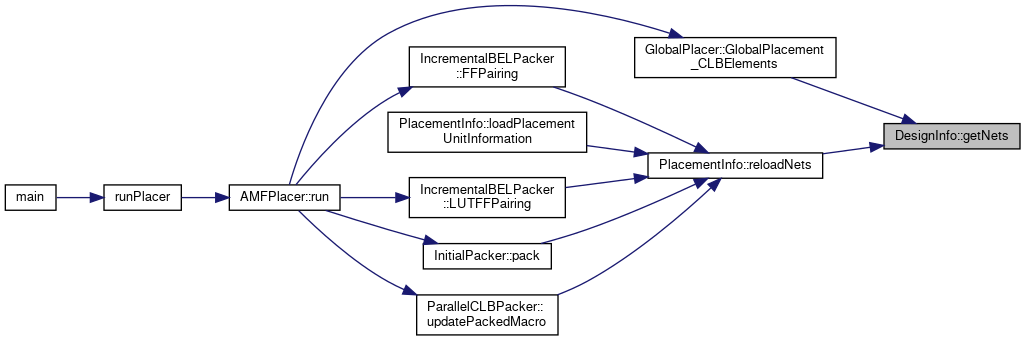

◆ getNets()

|

inline |

Definition at line 1613 of file DesignInfo.h.

Referenced by GlobalPlacer::GlobalPlacement_CLBElements(), and PlacementInfo::reloadNets().

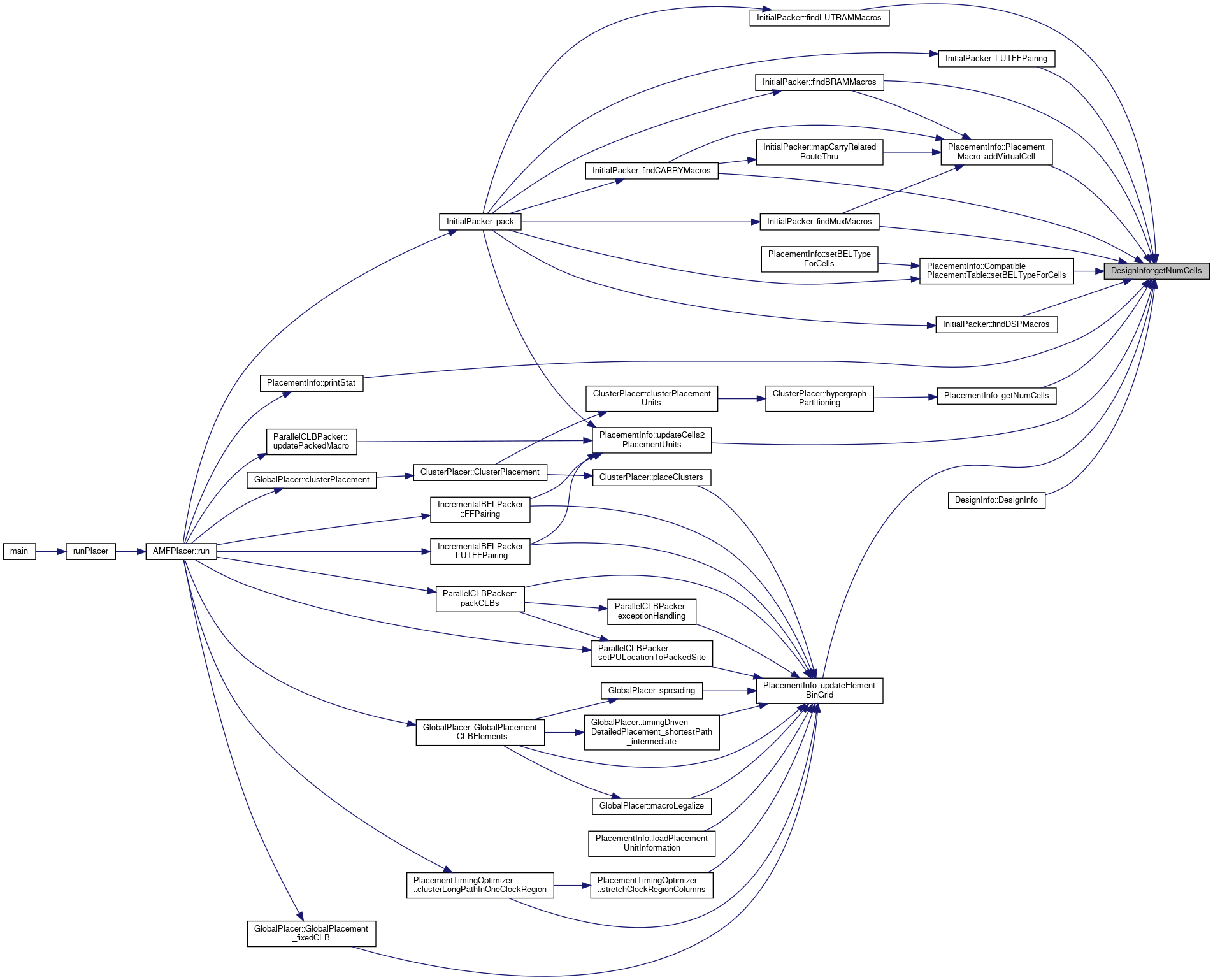

◆ getNumCells()

|

inline |

Definition at line 1600 of file DesignInfo.h.

Referenced by PlacementInfo::PlacementMacro::addVirtualCell(), DesignInfo(), InitialPacker::findBRAMMacros(), InitialPacker::findCARRYMacros(), InitialPacker::findDSPMacros(), InitialPacker::findLUTRAMMacros(), InitialPacker::findMuxMacros(), PlacementInfo::getNumCells(), InitialPacker::LUTFFPairing(), PlacementInfo::printStat(), PlacementInfo::CompatiblePlacementTable::setBELTypeForCells(), PlacementInfo::updateCells2PlacementUnits(), and PlacementInfo::updateElementBinGrid().

◆ getNumNets()

|

inline |

Definition at line 1604 of file DesignInfo.h.

Referenced by addPinToNet().

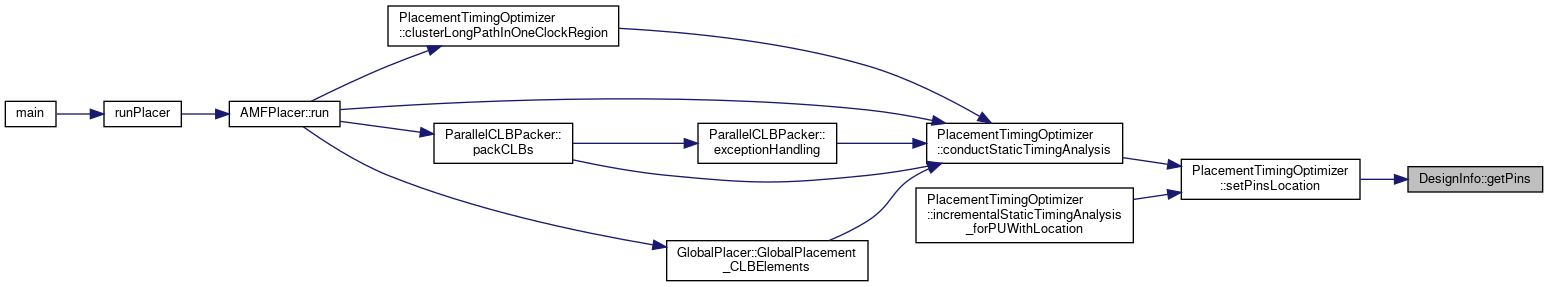

◆ getPins()

|

inline |

Definition at line 1617 of file DesignInfo.h.

Referenced by PlacementTimingOptimizer::setPinsLocation().

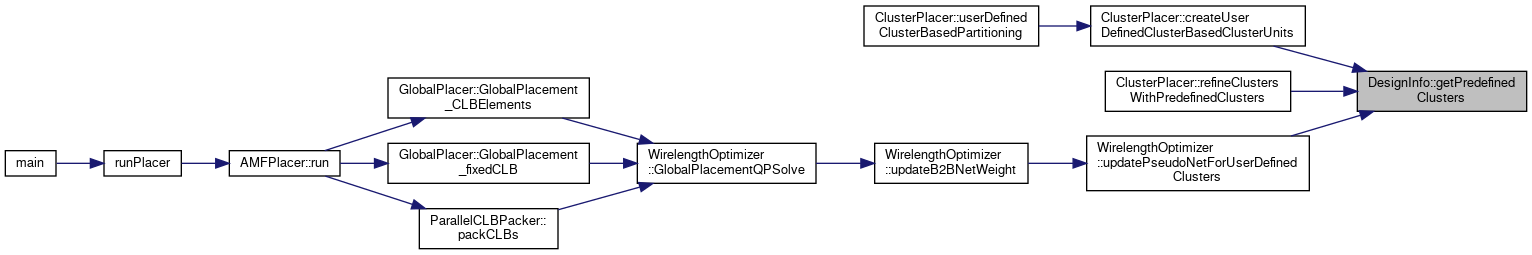

◆ getPredefinedClusters()

|

inline |

Get the predefined clusters which are defined in design configuration files.

- Returns

- std::vector<std::vector<DesignCell *>>&

Definition at line 1659 of file DesignInfo.h.

Referenced by ClusterPlacer::createUserDefinedClusterBasedClusterUnits(), ClusterPlacer::refineClustersWithPredefinedClusters(), and WirelengthOptimizer::updatePseudoNetForUserDefinedClusters().

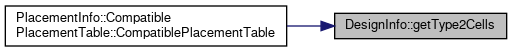

◆ getType2Cells()

|

inline |

Definition at line 1664 of file DesignInfo.h.

Referenced by PlacementInfo::CompatiblePlacementTable::CompatiblePlacementTable().

◆ isBRAM()

|

inlinestatic |

Definition at line 1341 of file DesignInfo.h.

Referenced by GlobalPlacer::dumpBRAMCoordinate(), MacroLegalizer::findMacroType2AvailableSites(), MacroLegalizer::findPossibleLegalLocation(), isLogicRelated(), and printStat().

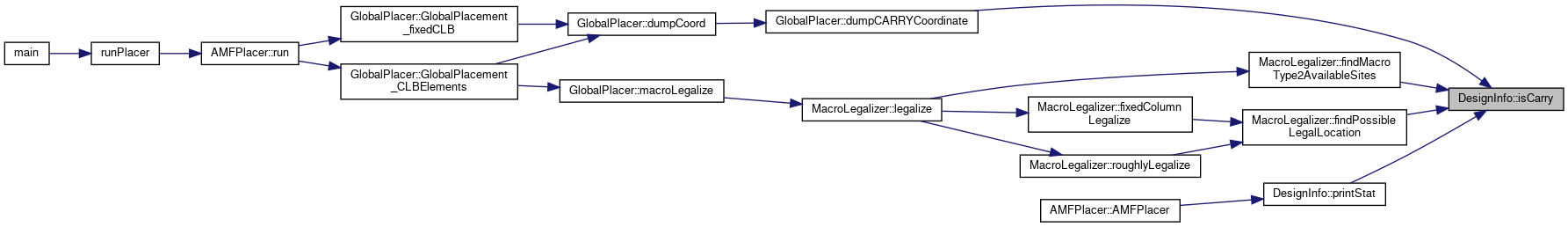

◆ isCarry()

|

inlinestatic |

Definition at line 1331 of file DesignInfo.h.

Referenced by GlobalPlacer::dumpCARRYCoordinate(), MacroLegalizer::findMacroType2AvailableSites(), MacroLegalizer::findPossibleLegalLocation(), and printStat().

◆ isClockBuffer()

|

inline |

Definition at line 1384 of file DesignInfo.h.

◆ isDesignClock()

|

inline |

check if a net is a global clock indicated by input design files

- Parameters

-

tmpNet target net

- Returns

- true if a net is a global clock indicated by input design files

- false if a net is NOT a global clock indicated by input design files

Definition at line 1713 of file DesignInfo.h.

Referenced by loadClocks().

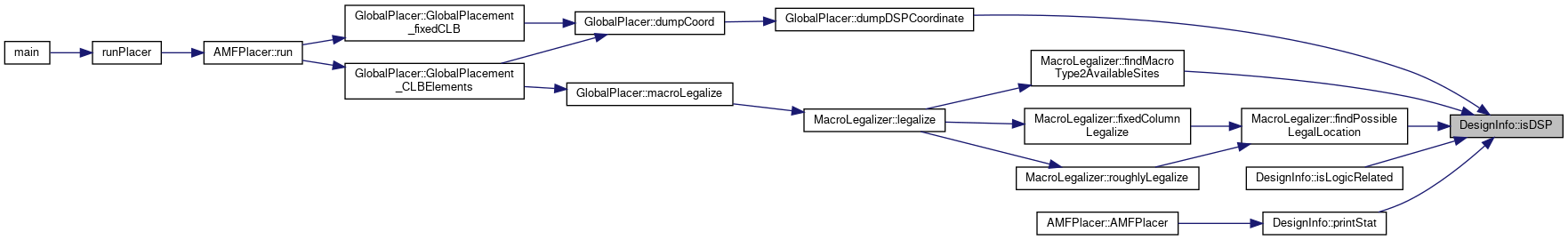

◆ isDSP()

|

inlinestatic |

Definition at line 1336 of file DesignInfo.h.

Referenced by GlobalPlacer::dumpDSPCoordinate(), MacroLegalizer::findMacroType2AvailableSites(), MacroLegalizer::findPossibleLegalLocation(), isLogicRelated(), and printStat().

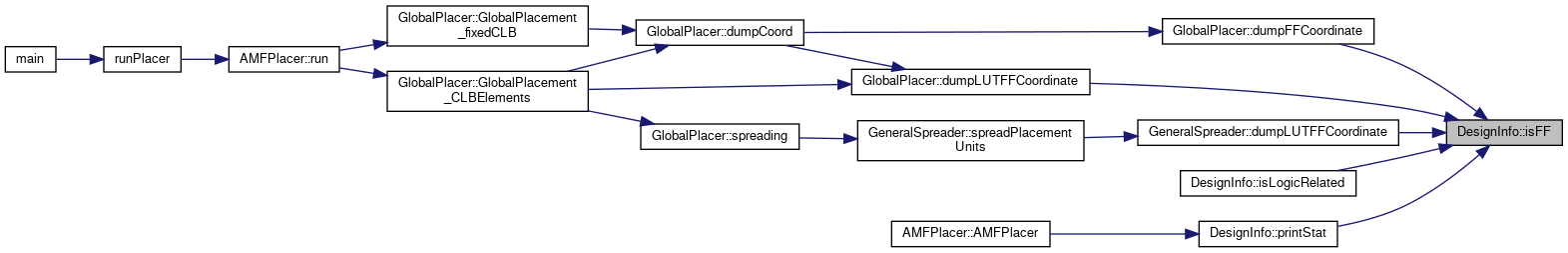

◆ isFF()

|

inlinestatic |

Definition at line 1360 of file DesignInfo.h.

Referenced by GlobalPlacer::dumpFFCoordinate(), GeneralSpreader::dumpLUTFFCoordinate(), GlobalPlacer::dumpLUTFFCoordinate(), isLogicRelated(), and printStat().

◆ isIO()

|

inlinestatic |

Definition at line 1366 of file DesignInfo.h.

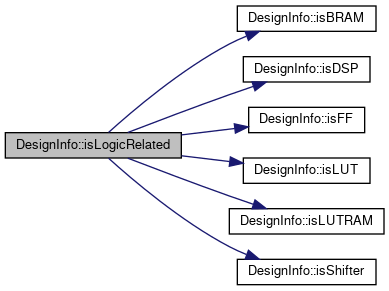

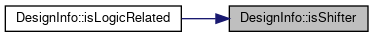

◆ isLogicRelated()

|

inline |

check whether the cell is related to logic computation

- Parameters

-

cellType a given cell type

- Returns

- true

- false

Definition at line 1401 of file DesignInfo.h.

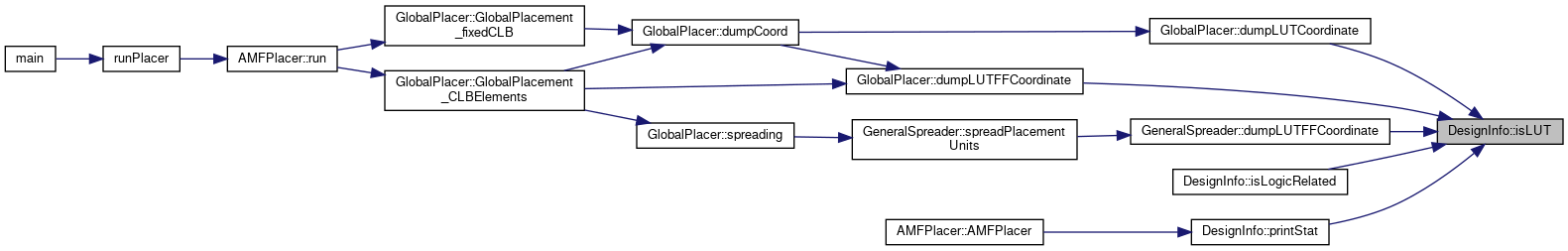

◆ isLUT()

|

inlinestatic |

Definition at line 1324 of file DesignInfo.h.

Referenced by GlobalPlacer::dumpLUTCoordinate(), GeneralSpreader::dumpLUTFFCoordinate(), GlobalPlacer::dumpLUTFFCoordinate(), isLogicRelated(), and printStat().

◆ isLUTRAM()

|

inlinestatic |

Definition at line 1352 of file DesignInfo.h.

Referenced by isLogicRelated(), and printStat().

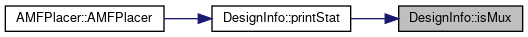

◆ isMux()

|

inlinestatic |

Definition at line 1347 of file DesignInfo.h.

Referenced by printStat().

◆ isShifter()

|

inline |

Definition at line 1389 of file DesignInfo.h.

Referenced by isLogicRelated().

◆ loadClocks()

| void DesignInfo::loadClocks | ( | std::string | clockFileName | ) |

load the global clock signals from a design information file

- Parameters

-

clockFileName

Definition at line 372 of file DesignInfo.cc.

Referenced by DesignInfo().

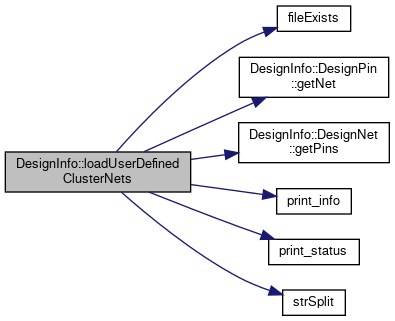

◆ loadUserDefinedClusterNets()

| void DesignInfo::loadUserDefinedClusterNets | ( | ) |

for user-defined-cluster-based optimization, load the nets in a user-defined cluster for later processing

Definition at line 484 of file DesignInfo.cc.

Referenced by DesignInfo().

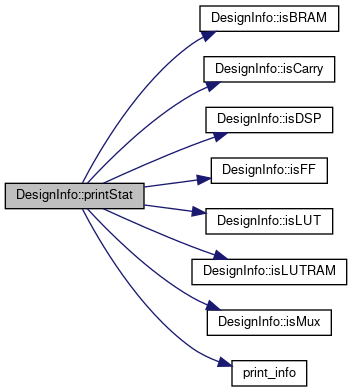

◆ printStat()

| void DesignInfo::printStat | ( | bool | verbose = false | ) |

Definition at line 635 of file DesignInfo.cc.

Referenced by AMFPlacer::AMFPlacer().

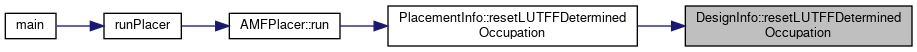

◆ resetLUTFFDeterminedOccupation()

|

inline |

reset the LUTFFDeterminedOccupation object

LUTFFDeterminedOccupation is used to record the final resource demand of a LUT/FF after final packing

Definition at line 1675 of file DesignInfo.h.

Referenced by PlacementInfo::resetLUTFFDeterminedOccupation().

◆ resetNetEnhanceRatio()

|

inline |

disable enhancement of all the nets in the design (reset extra weight to be 1)

Definition at line 1626 of file DesignInfo.h.

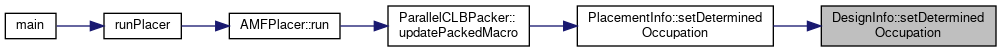

◆ setDeterminedOccupation()

|

inline |

Set the Determined Occupation of a specific cell.

LUTFFDeterminedOccupation is used to record the final resource demand of a LUT/FF after final packing

- Parameters

-

cellId target cell occupation resource demand of the cell after packing

Definition at line 1701 of file DesignInfo.h.

Referenced by PlacementInfo::setDeterminedOccupation().

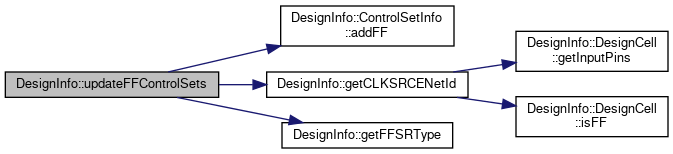

◆ updateFFControlSets()

| void DesignInfo::updateFFControlSets | ( | ) |

go through the FF cells to extract control sets for later processing

Definition at line 425 of file DesignInfo.cc.

Referenced by DesignInfo(), and InitialPacker::pack().

Member Data Documentation

◆ aliasNet2AliasNetId

|

private |

Definition at line 1745 of file DesignInfo.h.

Referenced by DesignInfo().

◆ cells

|

private |

Definition at line 1742 of file DesignInfo.h.

Referenced by addCell(), DesignInfo(), getCells(), getNumCells(), loadClocks(), printStat(), resetLUTFFDeterminedOccupation(), updateFFControlSets(), and ~DesignInfo().

◆ CLKSRCEFFType2ControlSetInfoId

|

private |

the mapping from the tuple of CLK/SR/CE ids and FF type to a unique defined control set id

Definition at line 1771 of file DesignInfo.h.

Referenced by DesignInfo(), and updateFFControlSets().

◆ clock2Cells

|

private |

the mapping from clocks to their corresponding cells driven by the clock net

Definition at line 1787 of file DesignInfo.h.

Referenced by DesignInfo(), getCellsUnderClock(), and loadClocks().

◆ clocks

|

private |

Definition at line 1780 of file DesignInfo.h.

Referenced by DesignInfo(), getClocksInDesign(), and loadClocks().

◆ clockSet

|

private |

Definition at line 1781 of file DesignInfo.h.

Referenced by DesignInfo(), isDesignClock(), and loadClocks().

◆ connectedPinsWithSmallNet

connected pin pairs by nets with a small number of pins

Definition at line 1759 of file DesignInfo.h.

Referenced by DesignInfo(), and loadUserDefinedClusterNets().

◆ controlSets

|

private |

Definition at line 1779 of file DesignInfo.h.

Referenced by DesignInfo(), enhanceFFControlSetNets(), getControlSets(), updateFFControlSets(), and ~DesignInfo().

◆ designArchievedTextFileName

|

private |

Definition at line 1790 of file DesignInfo.h.

Referenced by DesignInfo().

◆ DesignCellTypeStr

| std::vector<std::string> DesignInfo::DesignCellTypeStr {CELLTYPESTRS} |

Definition at line 194 of file DesignInfo.h.

Referenced by DesignInfo::ControlSetInfo::display(), fromStringToCellType(), and printStat().

◆ FFId2ControlSetId

|

private |

the mapping from FF IDs to a unique defined control set id

Definition at line 1777 of file DesignInfo.h.

Referenced by getFFControlSetId(), and updateFFControlSets().

◆ JSONCfg

|

private |

Definition at line 1789 of file DesignInfo.h.

Referenced by DesignInfo(), and loadUserDefinedClusterNets().

◆ LUTFFDeterminedOccupation

|

private |

LUTFFDeterminedOccupation is used to record the final resource demand of a LUT/FF after final packing.

Definition at line 1765 of file DesignInfo.h.

Referenced by getDeterminedOccupation(), resetLUTFFDeterminedOccupation(), and setDeterminedOccupation().

◆ name2Cell

|

private |

Definition at line 1746 of file DesignInfo.h.

Referenced by addCell(), DesignInfo(), getCell(), and loadUserDefinedClusterNets().

◆ name2Net

|

private |

Definition at line 1744 of file DesignInfo.h.

Referenced by addPinToNet(), DesignInfo(), getNet(), and loadClocks().

◆ netlist

|

private |

Definition at line 1741 of file DesignInfo.h.

Referenced by addPinToNet(), DesignInfo(), getNets(), getNumNets(), printStat(), resetNetEnhanceRatio(), and ~DesignInfo().

◆ pins

|

private |

Definition at line 1743 of file DesignInfo.h.

Referenced by DesignInfo(), and getPins().

◆ predefinedClusters

|

private |

the predefined clusters which are defined in design configuration files

Definition at line 1752 of file DesignInfo.h.

Referenced by getPredefinedClusters(), and loadUserDefinedClusterNets().

◆ type2Cells

|

private |

Definition at line 1753 of file DesignInfo.h.

Referenced by addCell(), DesignInfo(), getType2Cells(), and printStat().

The documentation for this class was generated from the following files:

- src/lib/HiFPlacer/designInfo/DesignInfo.h

- src/lib/HiFPlacer/designInfo/DesignInfo.cc