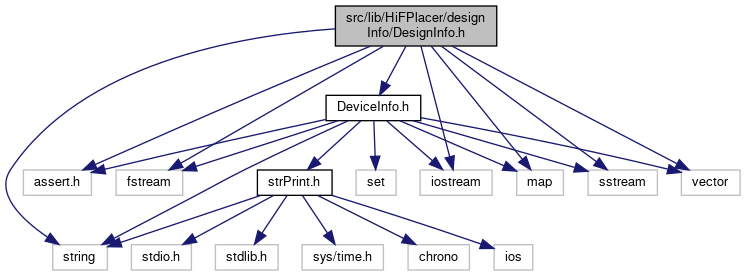

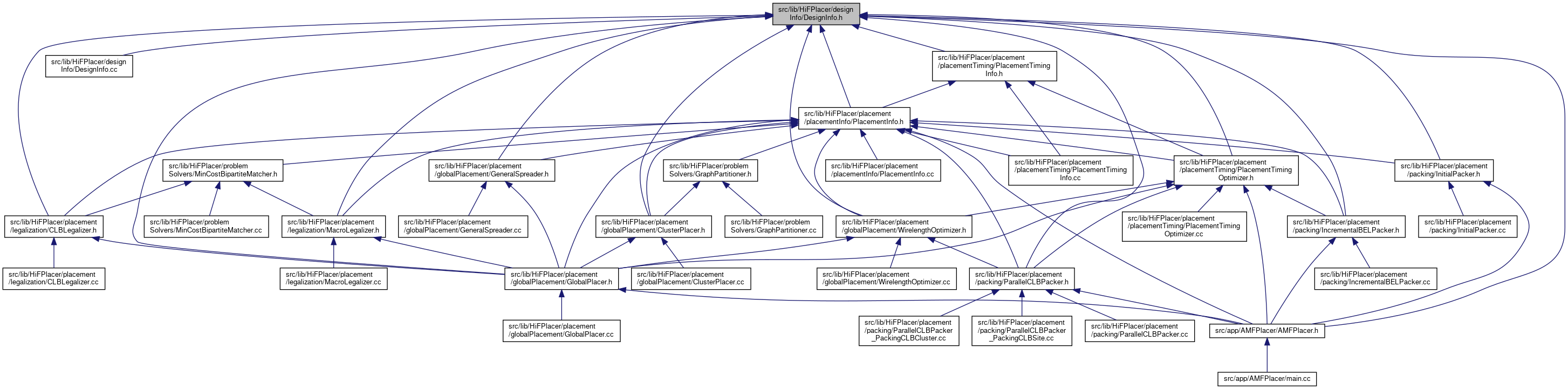

This header file contains the classes of data for a standalone design netlist. More...

#include "DeviceInfo.h"#include <assert.h>#include <fstream>#include <iostream>#include <map>#include <sstream>#include <string>#include <vector>

Go to the source code of this file.

Classes | |

| class | DesignInfo |

| Information related to FPGA designs, including design cells and their interconnections. More... | |

| class | DesignInfo::DesignElement |

| basic class of element in a design. More... | |

| class | DesignInfo::DesignPin |

| A design pin on a design cell connected to a net. More... | |

| class | DesignInfo::DesignNet |

| a design net (hyperedge) defined in the design, connecting to pins of cells More... | |

| class | DesignInfo::DesignCell |

| a DesignCell in design netlist, DesignPin objects of which might connect to DesignNet objects More... | |

| class | DesignInfo::ControlSetInfo |

| A control set is a combination of CLK, CE and SR signal. It could be nullptr (not related to control set) More... | |

Macros | |

| #define | CELLTYPESTRS |

Functions | |

| std::ostream & | operator<< (std::ostream &os, DesignInfo::DesignCell *cell) |

| std::ostream & | operator<< (std::ostream &os, DesignInfo::DesignPin *pin) |

Detailed Description

This header file contains the classes of data for a standalone design netlist.

- Version

- 0.1

- Date

- 2021-06-03

- Copyright

- Copyright (c) 2021 Reconfiguration Computing Systems Lab, The Hong Kong University of Science and Technology. All rights reserved.

Licensed under the Apache License, Version 2.0 (the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Definition in file DesignInfo.h.

Macro Definition Documentation

◆ CELLTYPESTRS

| #define CELLTYPESTRS |

Definition at line 38 of file DesignInfo.h.

Function Documentation

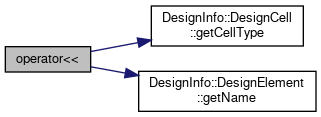

◆ operator<<() [1/2]

| std::ostream& operator<< | ( | std::ostream & | os, |

| DesignInfo::DesignCell * | cell | ||

| ) |

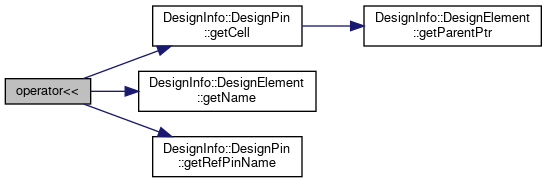

◆ operator<<() [2/2]

| std::ostream& operator<< | ( | std::ostream & | os, |

| DesignInfo::DesignPin * | pin | ||

| ) |